2 command/status address register (haccsar) – Renesas SH7781 User Manual

Page 1301

25. Audio Codec Interface (HAC)

Rev.1.00 Jan. 10, 2008 Page 1271 of 1658

REJ09B0261-0100

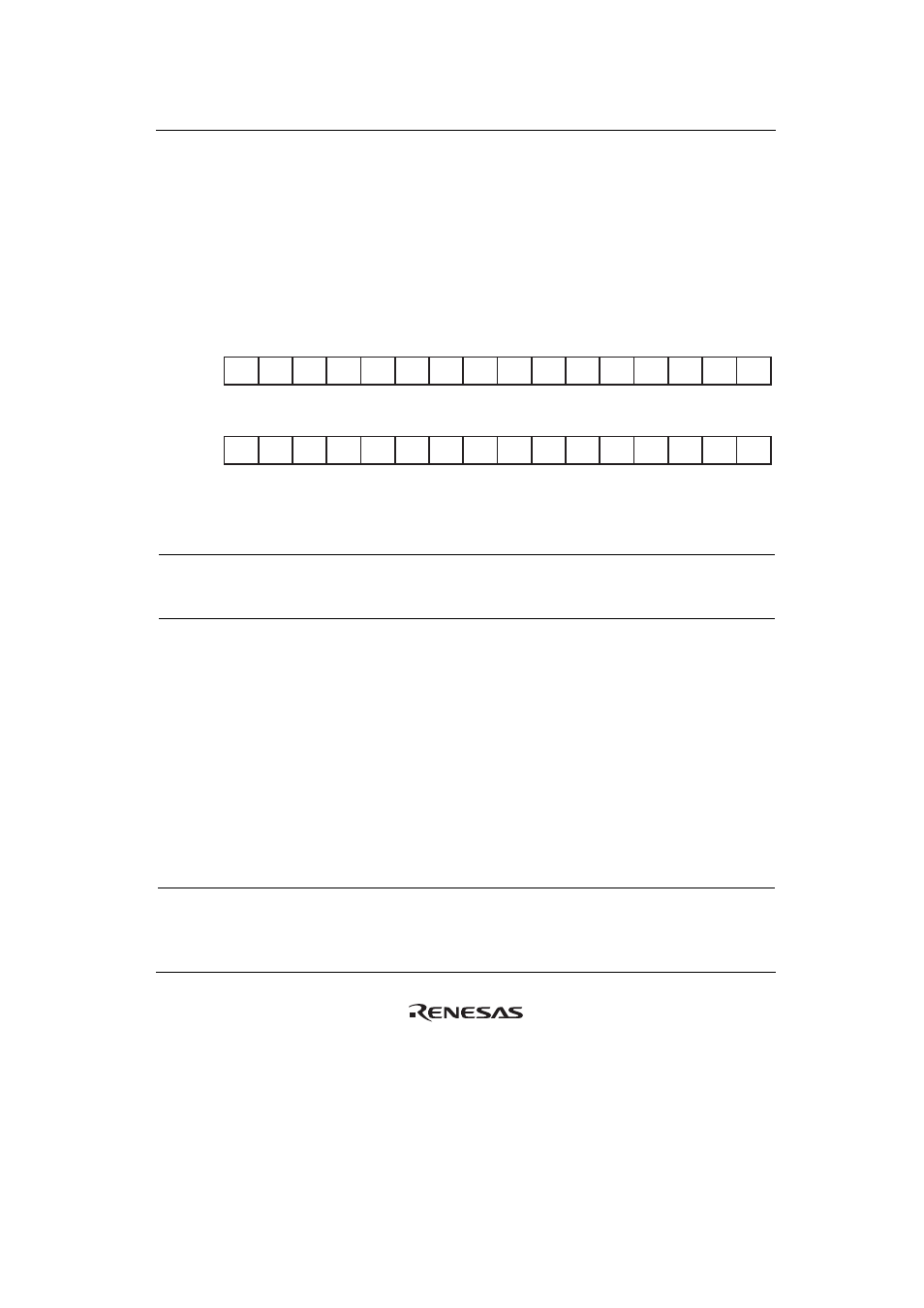

25.3.2

Command/Status Address Register (HACCSAR)

HACCSAR is a 32-bit read/write register that specifies the address of the codec register to be read

/written. When requesting a write to/read from a codec register, write the command register

address to HACCSAR and set the ST bit in the HACCR register to 1. The HAC then transmits this

register address to the codec via slot 1.

After the codec has responded to a read request (HACRSR.STARY = 1), the status address

received via slot 1 can be read out from HACCSAR.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

Bit:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Initial value:

R

R

R

R

R

R

R

R

R

R

R

R

R/W

R/W

R/W

R/W

R

R

R

R

R

R

R

R

R/W:

Bit:

Initial value:

R/W:

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R

R

R

R

CA3/

SA3

CA2/

SA2

CA1/

SA1

CA0/

SA0

SLR

EQ3

SLR

EQ4

SLR

EQ5

SLR

EQ6

SLR

EQ7

SLR

EQ8

SLR

EQ9

SLR

EQ10

SLR

EQ11

SLR

EQ12

CA6/

SA6

RW

CA5/

SA5

CA4/

SA4

0

Bit Bit

Name

Initial

Value R/W Description

31 to 20

⎯ All

0

R

Reserved

These bits are always read as 0. The write value should

always be 0.

19

RW

0

R/W

Codec Read/Write Command

0: Notifies the off-chip codec device of a write access to

the register specified in the address field (CA6/SA6

to CA0/SA0).

Write the data to HACCSDR in advance.

When HACACR.TX12_ATOMIC is 1, the HAC

transmits HACCSAR and HACCSDR as a pair in the

same TX frame.

When HACACR.TX12_ATOMIC is 0, transmission of

HACCSAR and HACCSDR in the same TX frame is

not guaranteed.

1: Notifies the off-chip codec device of a read access to

the register specified in the address field (CA6/SA6

to CA0/SA0).