Renesas SH7781 User Manual

Page 510

12. DDR2-SDRAM Interface (DBSC2)

Rev.1.00 Jan. 10, 2008 Page 480 of 1658

REJ09B0261-0100

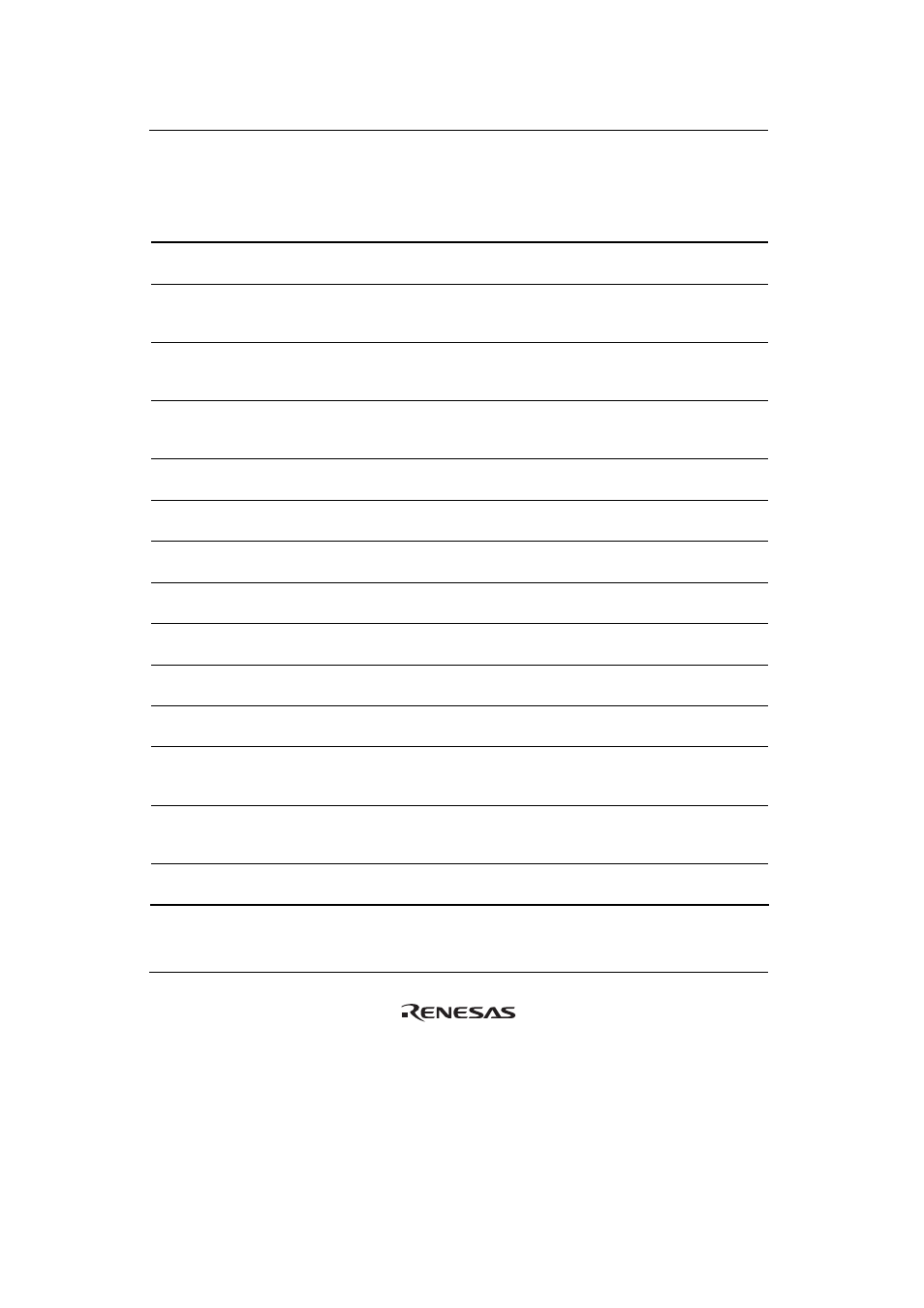

Table 12.9 DBSC2 Register Configuration

Register Name Abbreviation R/W P4 Area Address Area 7 Address

Access

Size

(Bits)

Synchroni-

zation

Clock

DBSC2 status

register

DBSTATE

R

H'FE80 000C

H'1E80 000C

32

DDRck

SDRAM

operation enable

register

DBEN

R/W H'FE80 0010

H'1E80 0010

32

DDRck

SDRAM

command

control register

DBCMDCNT

R/W H'FE80 0014

H'1E80 0014

32

DDRck

SDRAM

configuration

setting register

DBCONF

R/W H'FE80 0020

H'1E80 0020

32

DDRck

SDRAM timing

register 0

DBTR0

R/W H'FE80 0030

H'1E80 0030

32

DDRck

SDRAM timing

register 1

DBTR1

R/W H'FE80 0034

H'1E80 0034

32

DDRck

SDRAM timing

register 2

DBTR2

R/W H'FE80 0038

H'1E80 0038

32

DDRck

SDRAM refresh

control register 0

DBRFCNT0

R/W H'FE80 0040

H'1E80 0040

32

DDRck

SDRAM refresh

control register 1

DBRFCNT1

R/W H'FE80 0044

H'1E80 0044

32

DDRck

SDRAM refresh

control register 2

DBRFCNT2

R/W H'FE80 0048

H'1E80 0048

32

DDRck

SDRAM refresh

status register

DBRFSTS

R/W H'FE80 004C

H'1E80 004C

32

DDRck

DDRPAD

frequency

setting register

DBFREQ

R/W H'FE80 0050

H'1E80 0050

32

DDRck

DDRPAD DIC,

ODT, OCD

setting register

DBDICODTO

CD

R/W H'FE80 0054

H'1E80 0054

32

DDRck

SDRAM mode

setting register

DBMRCNT

W

H'FE80 0060

H'1E80 0060

32

DDRck