10 ready busy timeout counter (flbsycnt) – Renesas SH7781 User Manual

Page 1390

27. NAND Flash Memory Controller (FLCTL)

Rev.1.00 Jan. 10, 2008 Page 1360 of 1658

REJ09B0261-0100

27.3.10

Ready Busy Timeout Counter (FLBSYCNT)

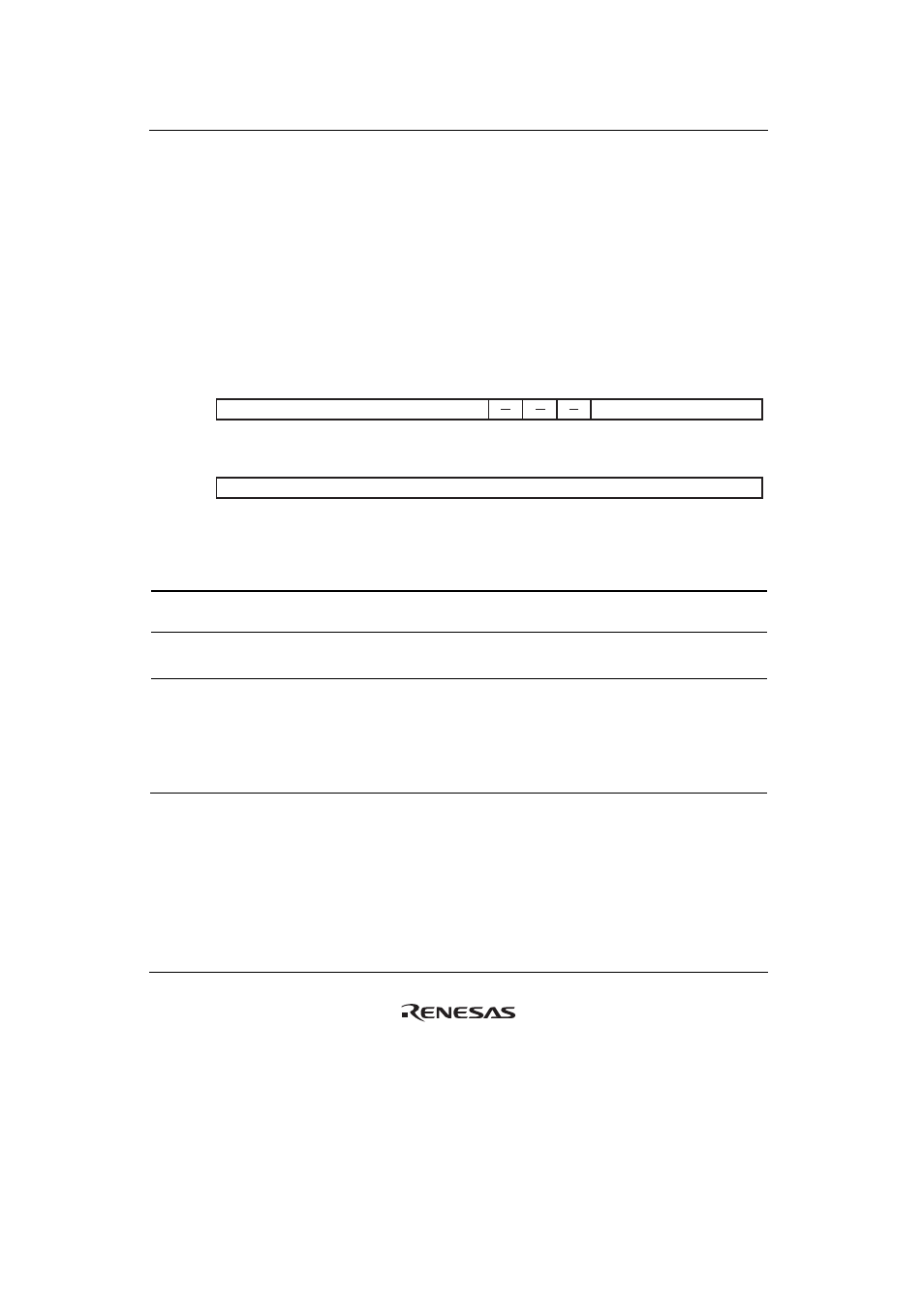

FLBSYCNT is a 32-bit read-only register.

The status of flash memory read by the status read is stored in the bits STAT7 to STAT0.

The timeout time set in bits RBTMOUT20 to RBTMOUT0 in FLBSYTMR is copied to bits

RBTIMCNT20 to RBTIMCNT0 and counting down is started when the FRB pin enters the busy

state. When values in bits RBTIMCNT20 to RBTIMCNT0 are decremented to 0, 1 the BTOERB

bit in FLINTDMACR is set to 1, and the occurrence of a timeout error is notified. In this case, an

FLSTE interrupt can be issued if an interrupt is enabled by the RBERINTE bit in FLINTDMACR.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Bit:

Initial value:

R/W:

Bit:

Initial value:

R/W:

STAT[7:0]

RBTIMCNT[20:16]

RBTIMCNT[15:0]

Bit Bit

Name

Initial

Value R/W Description

31 to 24 STAT[7:0]

H'00

R

Indicate the value obtained by the status read from

flash memory

23 to 21 —

All 0

R

Reserved

These bits are always read as 0.

20 to 0

RBTIMCNT[20:0] H'00000 R

Ready Busy Timeout Counter

When the FRB pin enters the busy state, the values

of bits RBTMOUT20 to RBTMOUT0 in FLBSYTMR

are copied to these bits. These bits are counted

down while the FRB pin is busy. A timeout error

occurs when these bits are decremented to 0.