4 register allocation of transfer data – Renesas SH7781 User Manual

Page 1163

22. Serial I/O with FIFO (SIOF)

Rev.1.00 Jan. 10, 2008 Page 1133 of 1658

REJ09B0261-0100

22.4.4

Register Allocation of Transfer Data

(1)

Transmit/Receive Data

Writing and reading of transmit/receive data is performed for the following registers.

• Transmit data writing: SITDR (32-bit access)

• Receive data reading: SIRDR (32-bit access)

Figure 22.5 shows the transmit/receive data and the SITDR and SIRDR bit alignment.

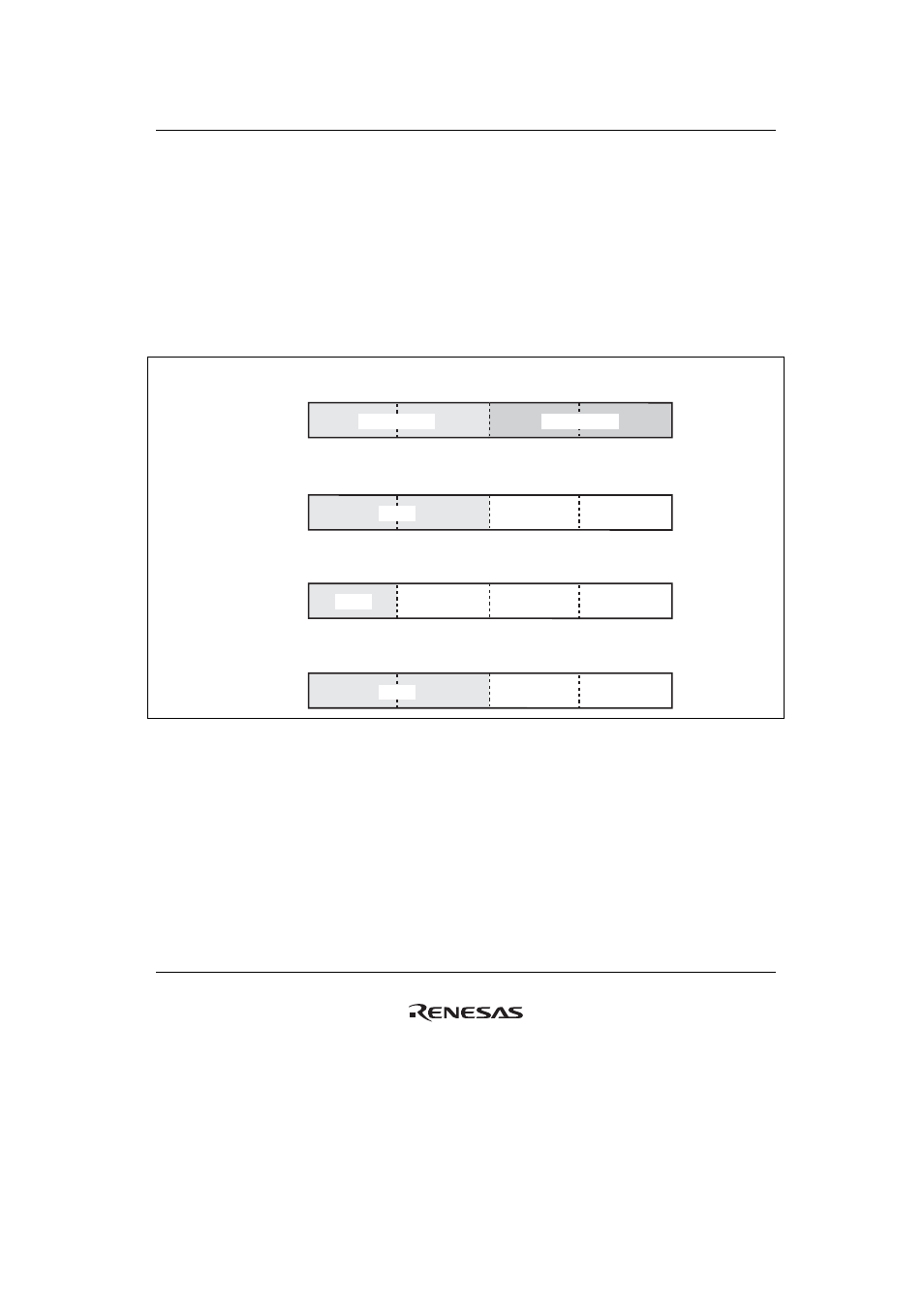

(a) 16-bit stereo data

(b) 16-bit monaural data

(c) 8-bit monaural data

(d) 16-bit stereo data (left and right same audio output)

31

24 23

16 15

8 7

0

31

24 23

16 15

8 7

0

31

24 23

16 15

8 7

0

31

24 23

16 15

8 7

0

L-channel data

Data

Data

Data

R-channel data

Figure 22.5 Transmit/Receive Data Bit Alignment

Note: In the figure, only the shaded areas are transmitted or received as valid data. Therefore,

access must be made in byte units for 8-bit data, and in word units for 16-bit data. Data in

not shaded areas is not transmitted or received.

Monaural or stereo can be specified for transmit data by the TDLE bit and TDRE bit in SITDAR.

Monaural or stereo can be specified for receive data by the RDLE bit and RDRE bit in SIRDAR.

To achieve left and right same audio output while stereo is specified for transmit data, set the

TLREP bit in SITDAR. Tables 22.8 and 22.9 show the audio mode specification for transmit data

and that for receive data, respectively.