Renesas SH7781 User Manual

Page 594

13. PCI Controller (PCIC)

Rev.1.00 Jan. 10, 2008 Page 564 of 1658

REJ09B0261-0100

(3)

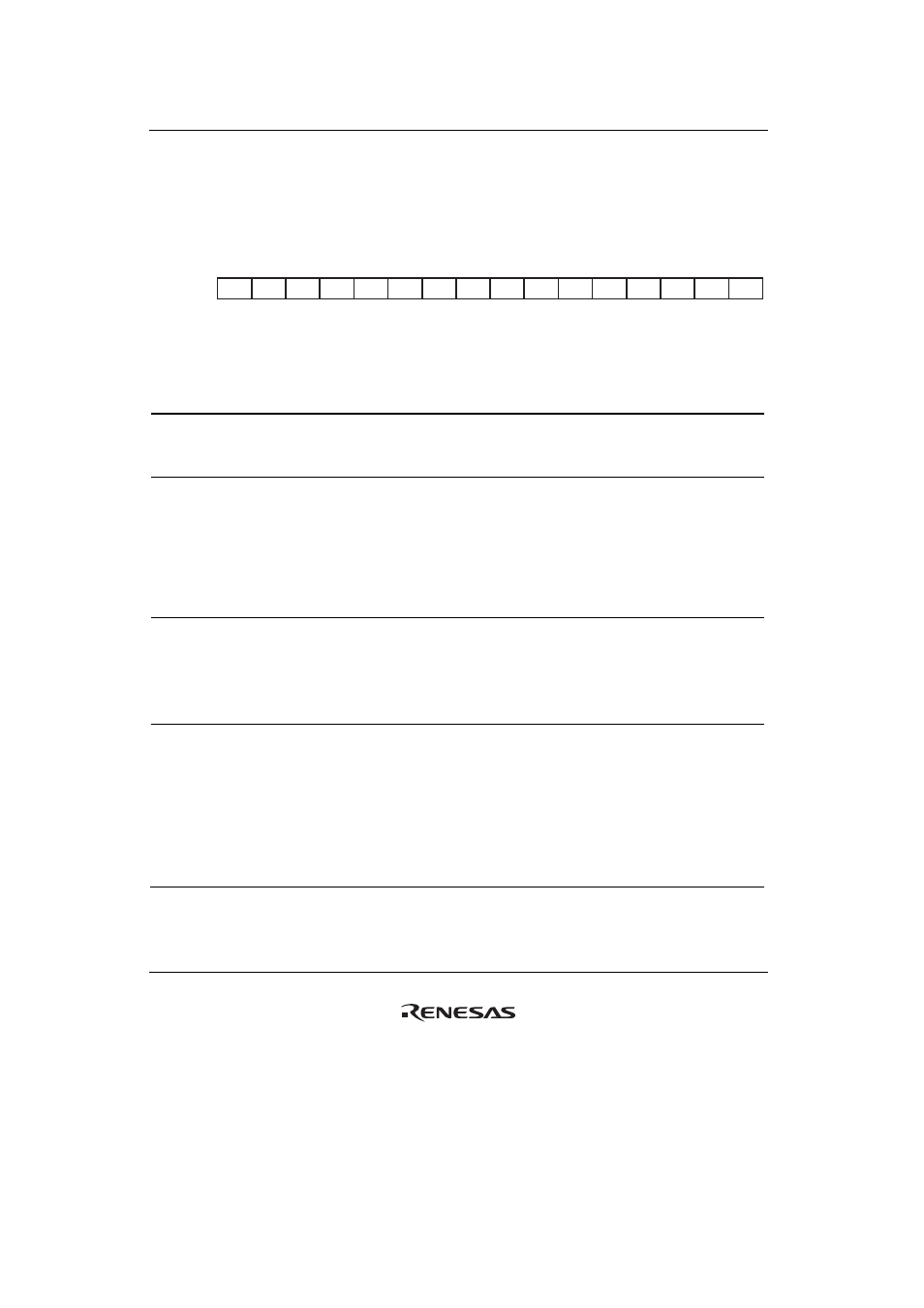

PCI Command Register (PCICMD)

PCICMD controls the basic functions of the PCIC to generate and respond to PCI cycles. When 0

is written to this register, this register ignores access commands from the external PCI device,

other than configuration access.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

IOS

MS

BM

SC

MWIE

VGAPS

PER

WCC

SERRE

FBBE

⎯

⎯

⎯

⎯

⎯

⎯

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R

R

R

R/W

R/W

R/W

R

R

R

R

R

R

R

Bit:

Initial value:

SH R/W:

R/W

R/W

R/W

R

R

R

R/W

R/W

R/W

R

R

R

R

R

R

R

PCI R/W:

Bit Bit

Name

Initial

Value R/W

Description

15 to 10

⎯

All 0

SH: R

PCI: R

Reserved

These bits are always read as 0. The write value

should always be 0.

9 FBBE

0

SH:

R

PCI: R

PCI Fast Back-to-Back Enable

Specifies whether fast back-to-back control is

performed on the different devices or not when the

PCIC is a master.

0: Enables fast back-to-back control for the same target

1: Enables fast back-to-back control for different targets

(not supported)

8 SERRE

0

SH:

R/W

PCI: R/W

SERR Output Control

Controls the

SERR output.

0:

SERR output disabled (pulled up by high impedance

and a pull-up resistor)

1:

SERR output enabled (SERR = low output)

7 WCC

1

SH:

R/W

PCI: R/W

Wait Cycle Control

Controls the address/data stepping.

When WCC is 1, both an address and data, only an

address, and only data are output at master write,

master read, and target read respectively for two clock

cycles.

0: Address/data stepping control disabled

1: Address/data stepping control enabled