Renesas SH7781 User Manual

Page 1410

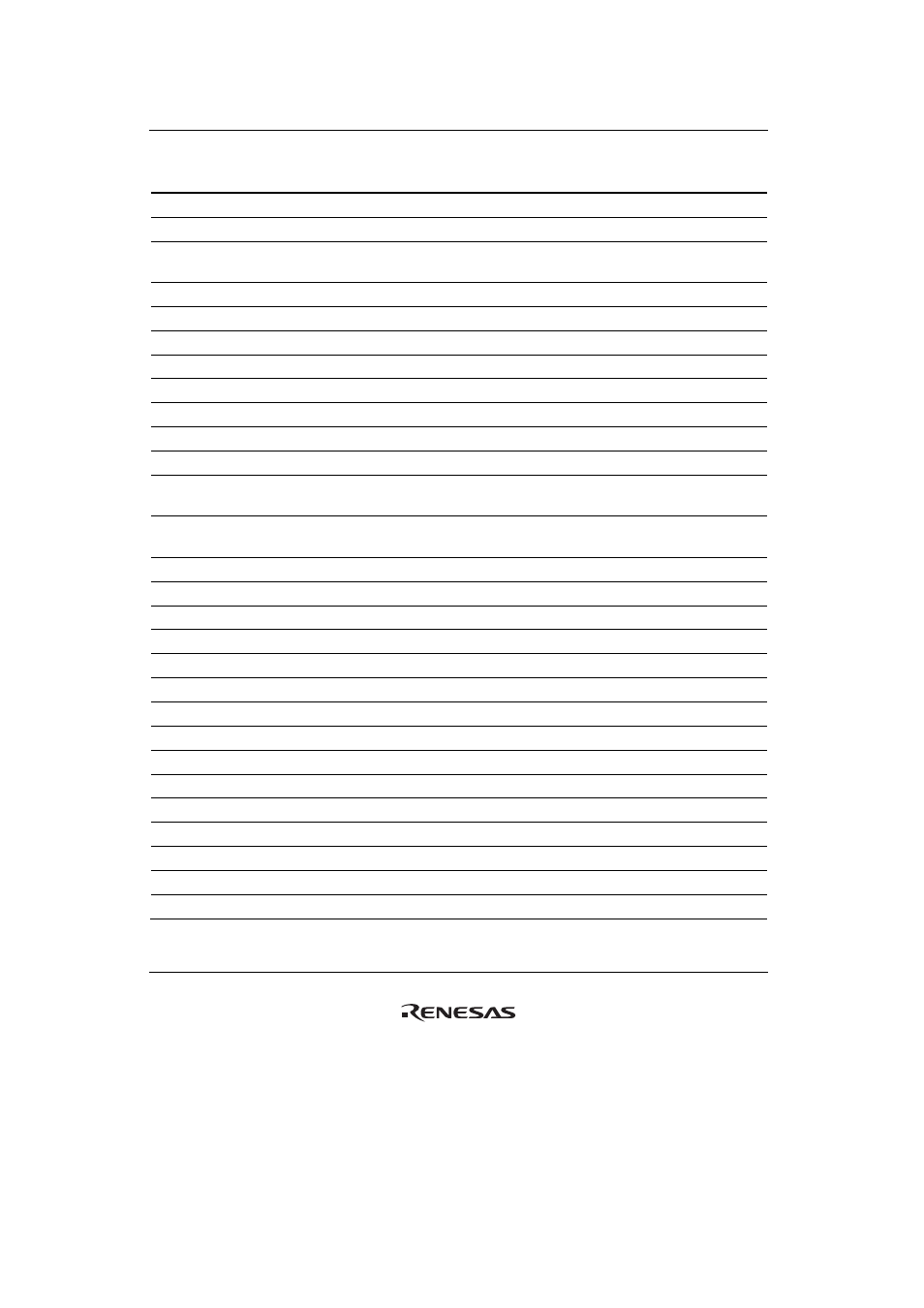

28. General Purpose I/O Ports (GPIO)

Rev.1.00 Jan. 10, 2008 Page 1380 of 1658

REJ09B0261-0100

Pin Name

Port GPIO

Selectable Module

GPIO

Interrupt

SCIF0_TXD/HSPI_TX/

FWE*

1

H

PH0

input/output

SCIF0/HSPI/FLCTL

⎯

SCIF5_TXD/HAC1_SYNC/SSI1_WS*

1

J

PJ7

input/output

SCIF5/HAC1/SSI1

⎯

SIOF_TXD/HAC0_SDOUT/

SSI0_SDATA*

1

J PJ6

input/output SCOF/HAC0/SSI0

⎯

SIOF_RXD/HAC0_SDIN/SSI0_SCK*

1

J

PJ5

input/output

SIOF/HAC0/SSI0

⎯

SIOF_SYNC/HAC0_SYNC/SSI0_WS*

1

J

PJ4

input/output

SIOF/HAC0/SSI0

⎯

SIOF_MCLK/

HAC_RES*

1

J

PJ3

input/output

SIOF/HAC

⎯

SIOF_SCK/HAC0_BITCLK/SSI0_CLK*

1

J

PJ2

input/output

SIOF/HAC0/SSI0

⎯

HAC1_BITCLK/SSI1_CLK*

1

J

PJ1

input/output

HAC1/SSI1

⎯

MODE13/TCLK/

IOIS16*

1

J

PJ0

input/output

—/TMU/LBSC

⎯

STATUS0

/DRAK0*

1

K PK7

input/output [STATUS]/DMAC

⎯

STATUS1

/DRAK1*

1

K PK6

input/output [STATUS]/DMAC

⎯

DACK2/SCIF2_TXD/MMCCMD/

SIOF_TXD*

1

K PK5

input/output DMAC/SCIF2/MMCIF/

SIOF

⎯

DACK3/SCIF2_SCK/MMCDAT/

SIOF_SCK*

1

K PK4

input/output DMAC/SCIF2/MMCIF/

SIOF

⎯

DREQ0

K PK3

input/output DMAC

⎯

DREQ1 K

PK2

input/output

DMAC

⎯

DACK0 K

PK1

input/output

DMAC

⎯

DACK1 K

PK0

input/output

DMAC

⎯

DREQ2/INTB*

1

L PL7

input/output DMAC/PCIC

Available

DREQ3/INTC*

1

L PL6

input/output DMAC/PCIC

Available

DRAK2/CE2A*

1

L PL5

input/output DMAC/LBSC

⎯

MODE0/

IRL4/FD4*

1

L

PL4

input/output

⎯/INTC/FLCTL

⎯

MODE1/

IRL5/FD5*

1

L

PL3

input/output

⎯/INTC/FLCTL

⎯

MODE2/

IRL6/FD6*

1

L

PL2

input/output

⎯/INTC/FLCTL

⎯

MODE3/

IRL7/FD7*

1

L

PL1

input/output

⎯/INTC/FLCTL

⎯

MODE12/

DRAK3/CE2B*

1

L

PL0

input/output

⎯/DMAC/LBSC

⎯

BREQ/BSACK M

PM1

input/output

LBSC

⎯

BACK/BSREQ M

PM0

input/output

LBSC

⎯

SCIF5_RXD/HAC1_SDIN/SSI1_SCK*

1

N

PN7

input/output

SCIF5/HAC1/SS1

⎯