3 register descriptions – Renesas SH7781 User Manual

Page 1132

22. Serial I/O with FIFO (SIOF)

Rev.1.00 Jan. 10, 2008 Page 1102 of 1658

REJ09B0261-0100

22.3

Register Descriptions

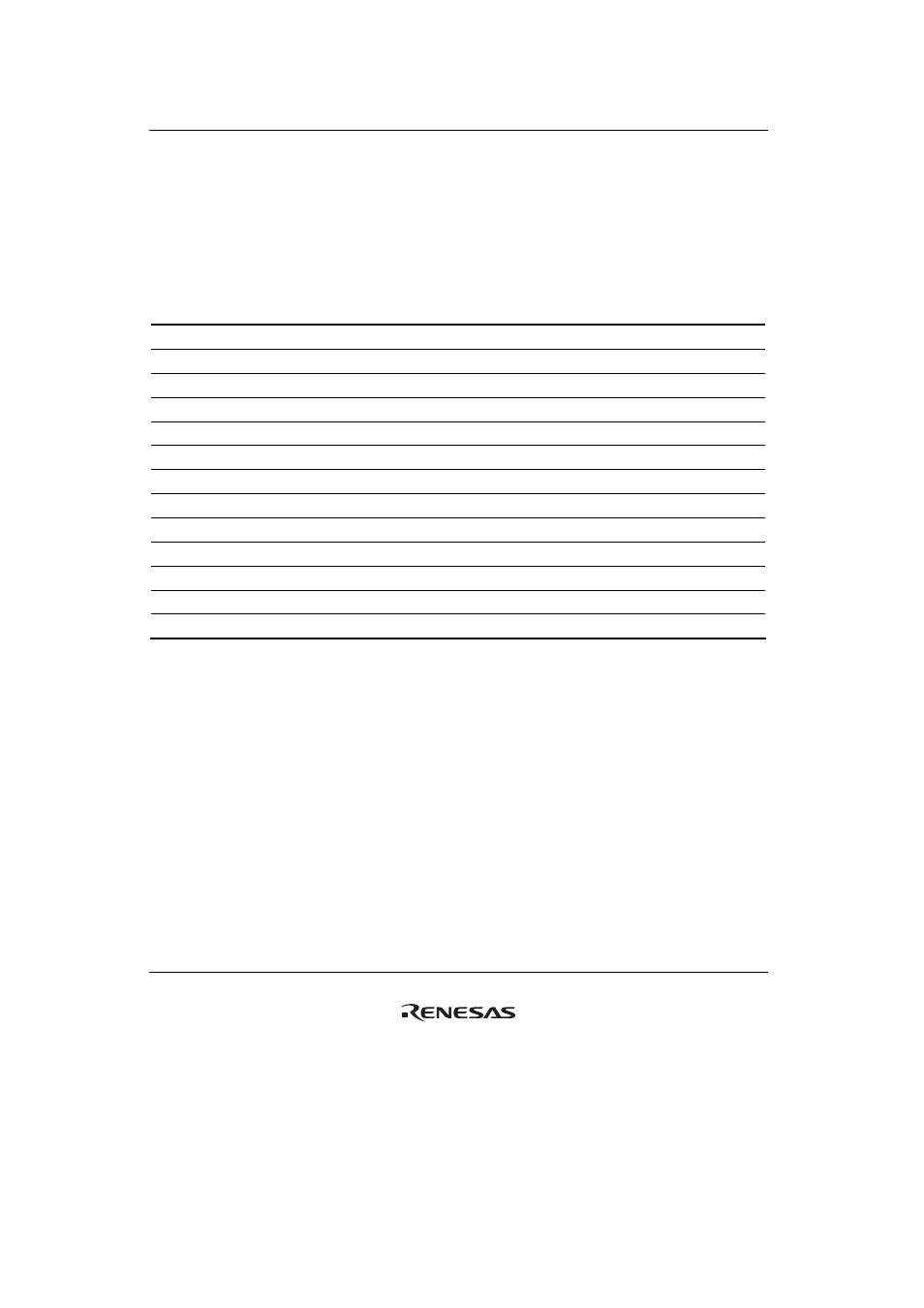

Table 22.2 shows the register configuration of the SIOF. Table 22.3 shows the register states in

each operating mode.

Table 22.2 Register Configuration

Name

Abbreviation R/W

P4 Address

Area7 Address

Access

Size

Sync

Clock

Mode register

SIMDR

R/W H'FFE2 0000 H'1FE2 0000 16

Pck

Clock select register

SISCR

R/W H'FFE2 0002 H'1FE2 0002 16

Pck

Transmit data assign register SITDAR

R/W H'FFE2 0004 H'1FE2 0004 16

Pck

Receive data assign register SIRDAR

R/W H'FFE2

0006 H'1FE2

0006 16

Pck

Control data assign register

SICDAR

R/W H'FFE2 0008 H'1FE2 0008 16

Pck

Control register

SICTR

R/W H'FFE2 000C H'1FE2 000C 16

Pck

FIFO control register

SIFCTR

R/W H'FFE2 0010 H'1FE2 0010 16

Pck

Status register

SISTR

R/W H'FFE2 0014 H'1FE2 0014 16

Pck

Interrupt enable register

SIIER

R/W H'FFE2 0016 H'1FE2 0016 16

Pck

Transmit data register

SITDR

W

H'FFE2 0020 H'1FE2 0020 32

Pck

Receive data register

SIRDR

R

H'FFE2 0024 H'1FE2 0024 32

Pck

Transmit control data register SITCR

R/W H'FFE2 0028 H'1FE2 0028 32

Pck

Receive control data register

SIRCR

R/W H'FFE2 002C H'1FE2 002C 32

Pck