Renesas SH7781 User Manual

Page 744

14. Direct Memory Access Controller (DMAC)

Rev.1.00 Jan. 10, 2008 Page 714 of 1658

REJ09B0261-0100

• Intermittent mode 16 (DMAOR. CMS = 10, CHCR.LCKN = 0 or 1, CHCR.TB = 0)

• Intermittent mode 64 (DMAOR. CMS = 11, CHCR.LCKN = 0 or 1, CHCR.TB = 0)

In intermittent mode of cycle steal, the DMAC gives the SuperHyway bus mastership to other

bus master whenever a one-transfer unit (byte, word, longword, or 16-byte or 32-byte unit) is

completed. After that, if the next transfer request occurs, the DMAC issues the next transfer

request after waiting for 16 or 64 clocks in Bck, transfers data of one-transfer unit again, and

returns the SuperHyway bus mastership to other bus master. These operations are repeated

until the transfer end condition is satisfied. It is possible to make lower the ratio of bus

occupation by DMA transfer than cycle steal normal modes 1 and 2.

When the DMAC issues the next transfer request again, DMA transfer can be postponed in

case of entry updating due to cache miss.

The intermittent modes must be cycle steal mode in all channels (channels 0 to 5)

corresponding to DMAOR0 or all channels (channels 6 to11) corresponding to DMAOR1.

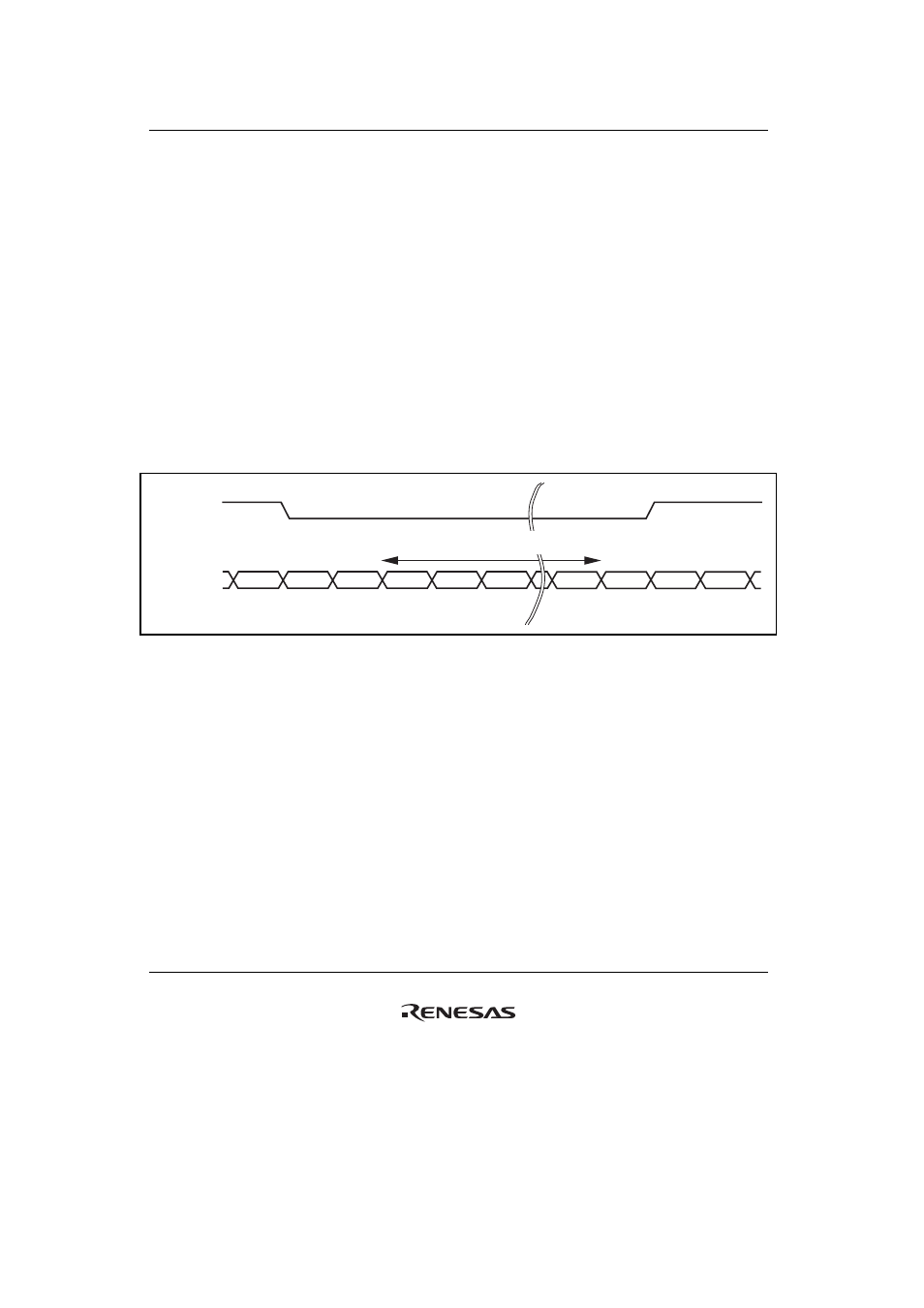

Figure 14.8 shows an example of DMA transfer timing in cycle steal intermittent mode.

DREQ

SuperHyway

bus cycle

Read/Write

Read/Write

CPU

CPU

CPU

DMAC

DMAC

CPU

CPU

DMAC

DMAC

CPU

More than 16 or 64 Bck

(depends on DMAOR.CMS settings)

Figure 14.8 Example e of DMA Transfer Timing in Cycle Steal Intermittent Mode

(DREQ Low Level Detection)

(b)

Burst Mode (CHCR.LCKN

= 1, CHCR.TB = 1)

In burst mode, once the DMAC obtains the SuperHyway bus mastership, the transfer is performed

continuously without releasing the bus mastership until the transfer end condition is satisfied. If

the DREQ is detected at level in external request mode, when the DREQ pin is not active, the

DMAC passes bus mastership to the other bus master after the DMAC transfer request that has

already been accepted ends, even if the transfer end conditions have not been satisfied.

Burst mode is not available when an on-chip peripheral module is the transfer request source.

Burst mode can be set for only channels 0 to 5.

Figure 14.9 shows DMA transfer timing in burst mode.