Renesas SH7781 User Manual

Page 497

12. DDR2-SDRAM Interface (DBSC2)

Rev.1.00 Jan. 10, 2008 Page 467 of 1658

REJ09B0261-0100

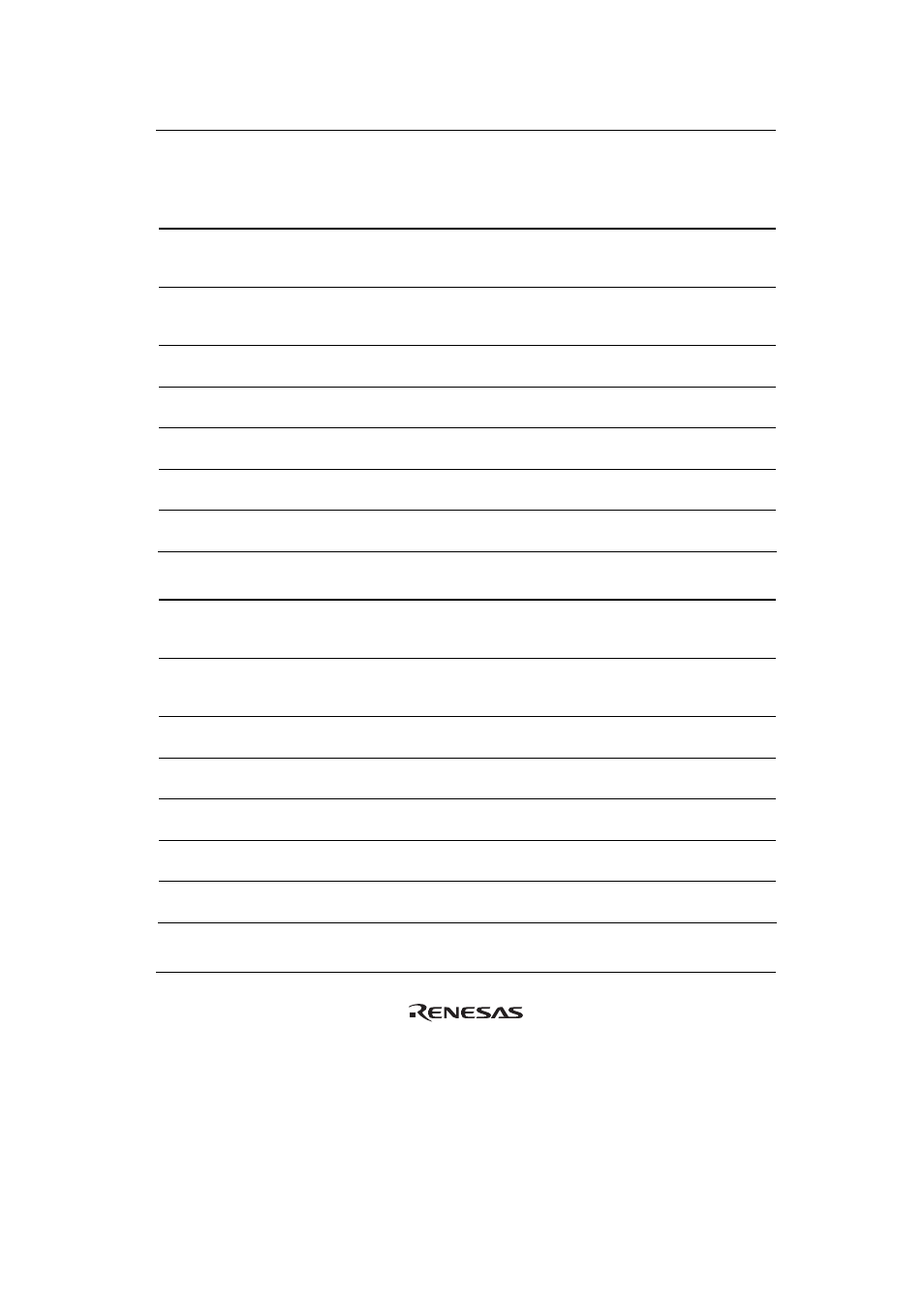

Table 12.3 Positions of Valid Data for Access with Burst Length of 4, when the External

Data Bus Width Is Set to 32 Bits

(1) Little Endian

First Access

Second Access

Third Access

Fourth Access

Byte access

(address 8n +

0,1,2,3)

Invalid Valid Invalid Invalid

Byte access

(address 8n +

4,5,6,7)

Valid Invalid Invalid Invalid

Word access

(address 8n + 0,2)

Invalid Valid Invalid Invalid

Word access

(address 8n + 4,6)

Valid Invalid Invalid Invalid

Longword access

(address 8n + 0)

Invalid Valid Invalid Invalid

Longword access

(address 8n + 4)

Valid Invalid Invalid Invalid

Quadword access

(address 8n + 0)

Valid Valid Invalid

Invalid

(2) Big Endian

First Access

Second Access

Third Access

Fourth Access

Byte access

(address 8n +

0,1,2,3)

Valid Invalid Invalid Invalid

Byte access

(address 8n +

4,5,6,7)

Invalid Valid Invalid Invalid

Word access

(address 8n + 0,2)

Valid Invalid Invalid Invalid

Word access

(address 8n + 4,6)

Invalid Valid Invalid Invalid

Longword access

(address 8n + 0)

Valid Invalid Invalid Invalid

Longword access

(address 8n + 4)

Invalid Valid Invalid Invalid

Quadword access

(address 8n + 0)

Valid Valid Invalid

Invalid