Renesas SH7781 User Manual

Page 326

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 296 of 1658

REJ09B0261-0100

(11)

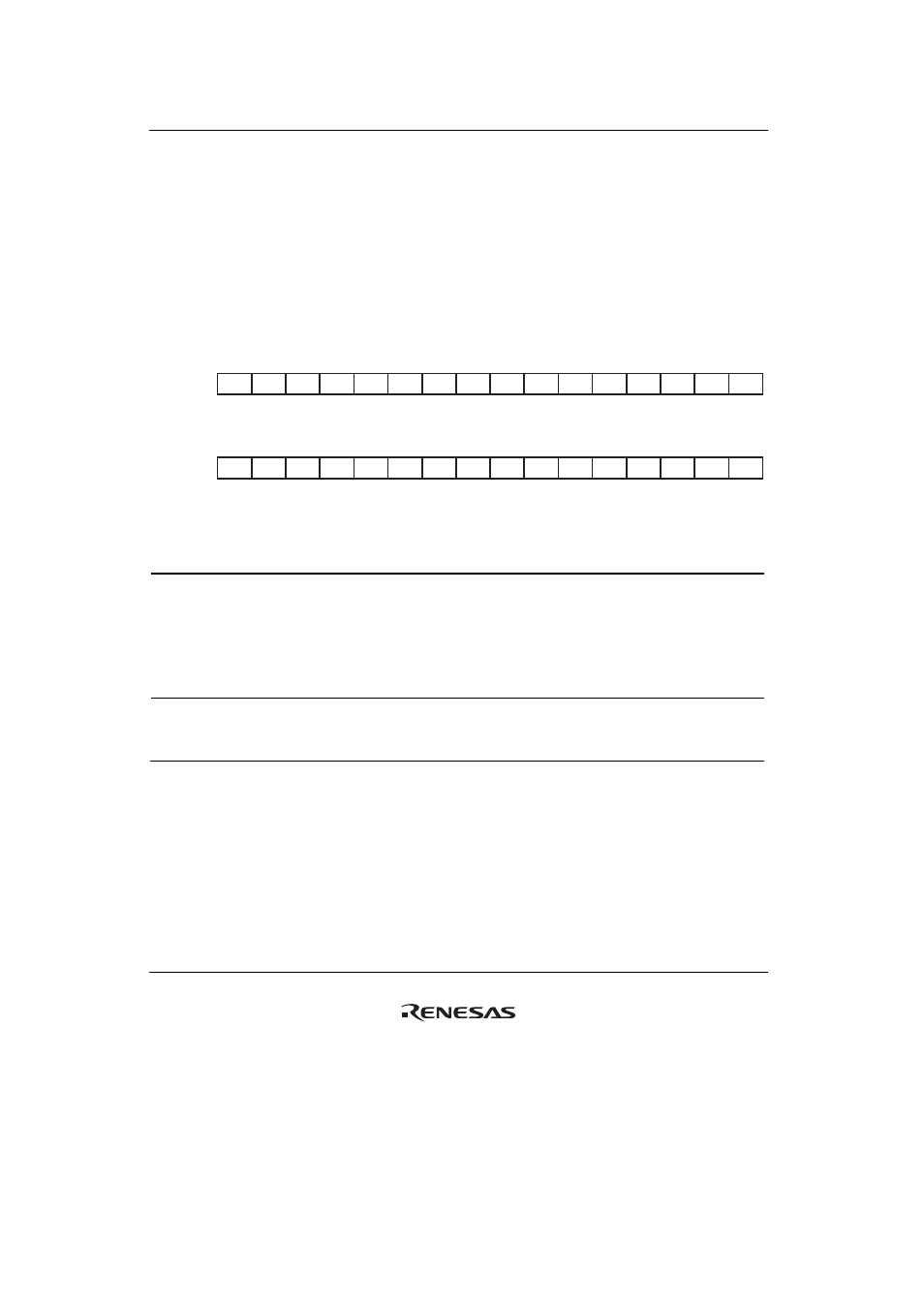

NMI Flag Control Register (NMIFCR)

NMIFCR is a 32-bit readable and conditionally writable register that has an NMI flag (NMIFL

bit). The NMIFL bit is automatically set to 1 when an NMI interrupt is detected by the INTC.

Writing 0 to the NMIFL bit clears it.

The value of the NMIFL bit does not affect acceptance of the NMI by the CPU. Although an NMI

request detected by the INTC is cleared when the CPU accepts the NMI, the NMIFL bit is not

cleared automatically. Even if 0 is written to the NMIFL bit before the NMI request is accepted by

the CPU, the NMI request is not canceled.

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

0

0

0

0

0

0

0

0

0

0

0

0

0

0

x

0

NMIFL

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

NMIL

⎯

R/(W)

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Bit:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Bit:

Initial value:

R/W:

Bit Name

Initial

Value R/W

Description

31

NMIL

x

R

NMI Input Level

Indicates the level of the signal input to the NMI pin;

that is, this bit is read to determine the level on the NMI

pin. This bit cannot be modified.

0: The low level is being input to the NMI pin

1: The high level is being input to the NMI pin

30 to 17 —

All 0

R

Reserved

These bits are always read as 0. The write value

should always be 0.