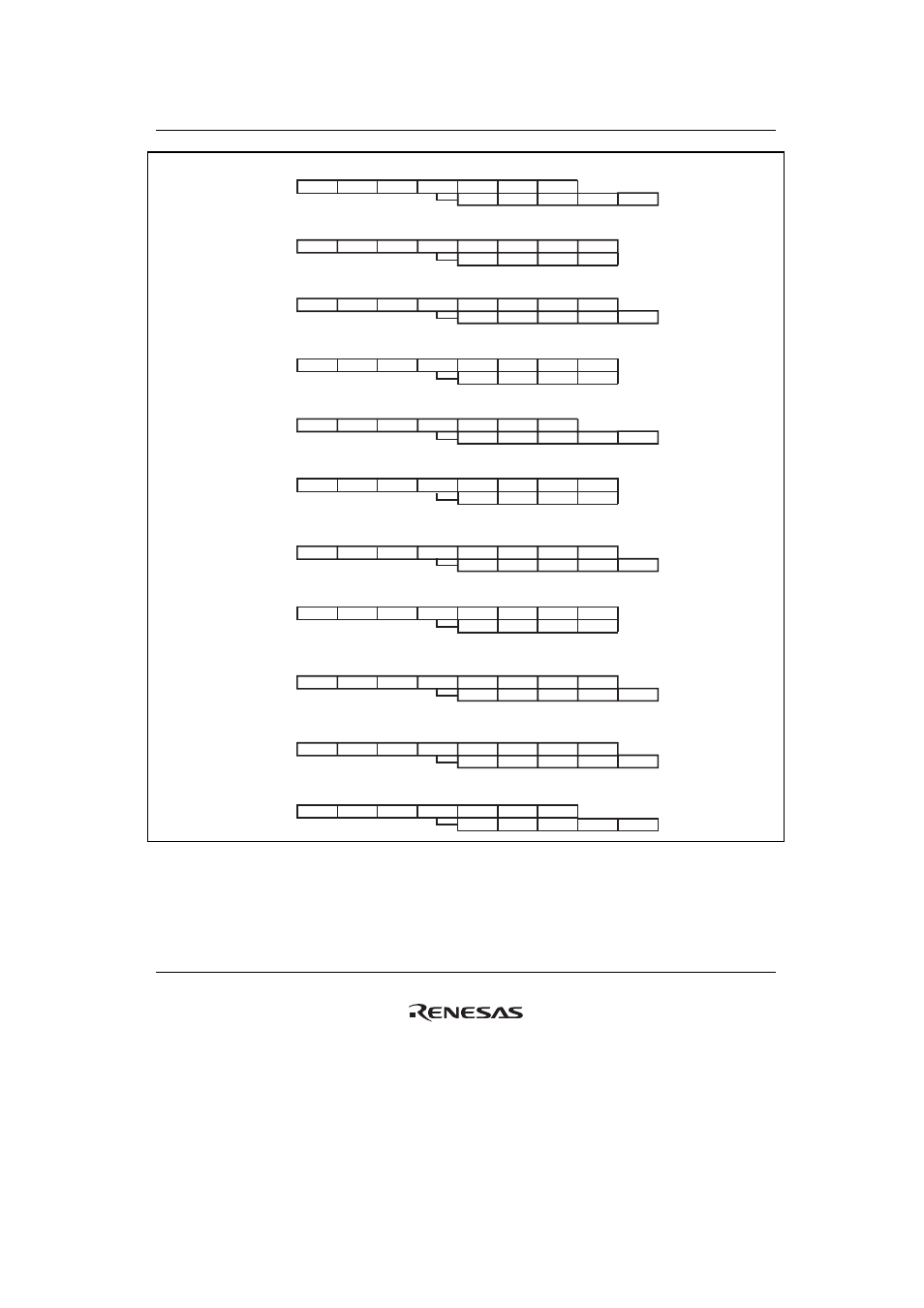

Figure 4.2 instruction execution patterns (7) – Renesas SH7781 User Manual

Page 103

4. Pipelining

Rev.1.00 Jan. 10, 2008 Page 73 of 1658

REJ09B0261-0100

I1

I2

I3

ID

s1

s2

s3

s1

s2

s3

WB

s1

s2

s3

WB

FS1

FS2

FS3

FS4

FS1

FS2

FS3

FS4

FS

FS1

FS2

FS3

FS4

FS1

FS2

FS3

FS4

FS1

FS2

FS3

FS4

FS

FS1

FS2

FS3

FS4

FS

FS1

FS2

FS3

FS4

FS1

FS2

FS3

FS4

FS

FS1

FS2

FS3

FS4

FS

I3

I3

I3

I3

I3

I3

I3

I3

I3

I3

I1

I2

ID

I1

I2

ID

S1

S2

S3

WB

S1

S2

S3

S1

S2

S3

WB

I1

I2

ID

s1

s2

s3

I1

I2

ID

WB

S1

S2

S3

WB

FS1

FS2

FS3

FS4

S1

S2

S3

WB

FS1

FS2

FS3

FS4

FS

s1

s2

s3

WB

I1

I2

ID

I1

I2

ID

I1

I2

ID

I1

I2

ID

I1

I2

ID

I1

I2

ID

s1

s2

s3

FS

(6-1) LDS to FPUL: 1 issue cycle

(6-2) STS from FPUL: 1 issue cycle

(6-3) LDS.L to FPUL: 1 issue cycle

(6-4) STS.L from FPUL: 1 issue cycle

(6-5) LDS to FPSCR: 1 issue cycle

(6-6) STS from FPSCR: 1 issue cycle

(6-7) LDS.L to FPSCR: 1 issue cycle

(6-8) STS.L from FPSCR: 1 issue cycle

(6-9) FPU load/store instruction FMOV: 1 issue cycle

(6-10) FLDS: 1 issue cycle

(6-11) FSTS: 1 issue cycle

Figure 4.2 Instruction Execution Patterns (7)

- Single-Chip Microcomputer M34551T2-MCU (42 pages)

- M3T-FLX-80NRA (6 pages)

- 70 (162 pages)

- M16C/30P (102 pages)

- PROM Programming Adapter PCA7427G02 (20 pages)

- R0E572110CFK00 (40 pages)

- H8/325 Series (20 pages)

- Single-Chip Microcomputer H8/36079 (27 pages)

- Direct Dummy IC M3T-DIRECT100S (4 pages)

- M3A-2152 (95 pages)

- PCA7755D (6 pages)

- M16C/6N5 (106 pages)

- SH7085 (50 pages)

- QFP-144 (23 pages)

- H8/3834 Series (22 pages)

- RSKM16C62P (3 pages)

- H8/33937 (22 pages)

- Single-Chip Microcomputer H8SX/1622 (5 pages)

- E6000 (29 pages)

- PCA7400 (18 pages)

- PCA4738FF-64 (20 pages)

- SuperH HS7339KCU01HE (43 pages)

- M16C FAMILY (103 pages)

- PCA7412F-100 (20 pages)

- 4513 (210 pages)

- M34551E8FP (16 pages)

- Dummy IC M3T-SSOP36B-450 (4 pages)

- Emulation Pod M30100T3-RPD-E (52 pages)

- Converter Board for M30102 M30102T-PTC (4 pages)

- SH7145 (31 pages)

- HS1653ECN61H (36 pages)

- Converter Board R0E521276CFG00 (4 pages)

- PCA7302E1F-80 (18 pages)

- H8/3814 Series (21 pages)

- H8S/2646 Series (20 pages)

- SuperHTM Family SH7125 Series (40 pages)

- M30262T-PTC (4 pages)

- SH7670 (82 pages)

- H8/3864 Series (20 pages)

- Emulator System M3T-MR100 (306 pages)

- 38K0 (6 pages)

- PLQP0176KB-A (40 pages)

- Direct Dummy IC M3T-DIRECT80S (6 pages)

- PCA4738L-80A (26 pages)

- Converter Board R0E5212BACFG00 (6 pages)