11 sdram refresh status register (dbrfsts) – Renesas SH7781 User Manual

Page 534

12. DDR2-SDRAM Interface (DBSC2)

Rev.1.00 Jan. 10, 2008 Page 504 of 1658

REJ09B0261-0100

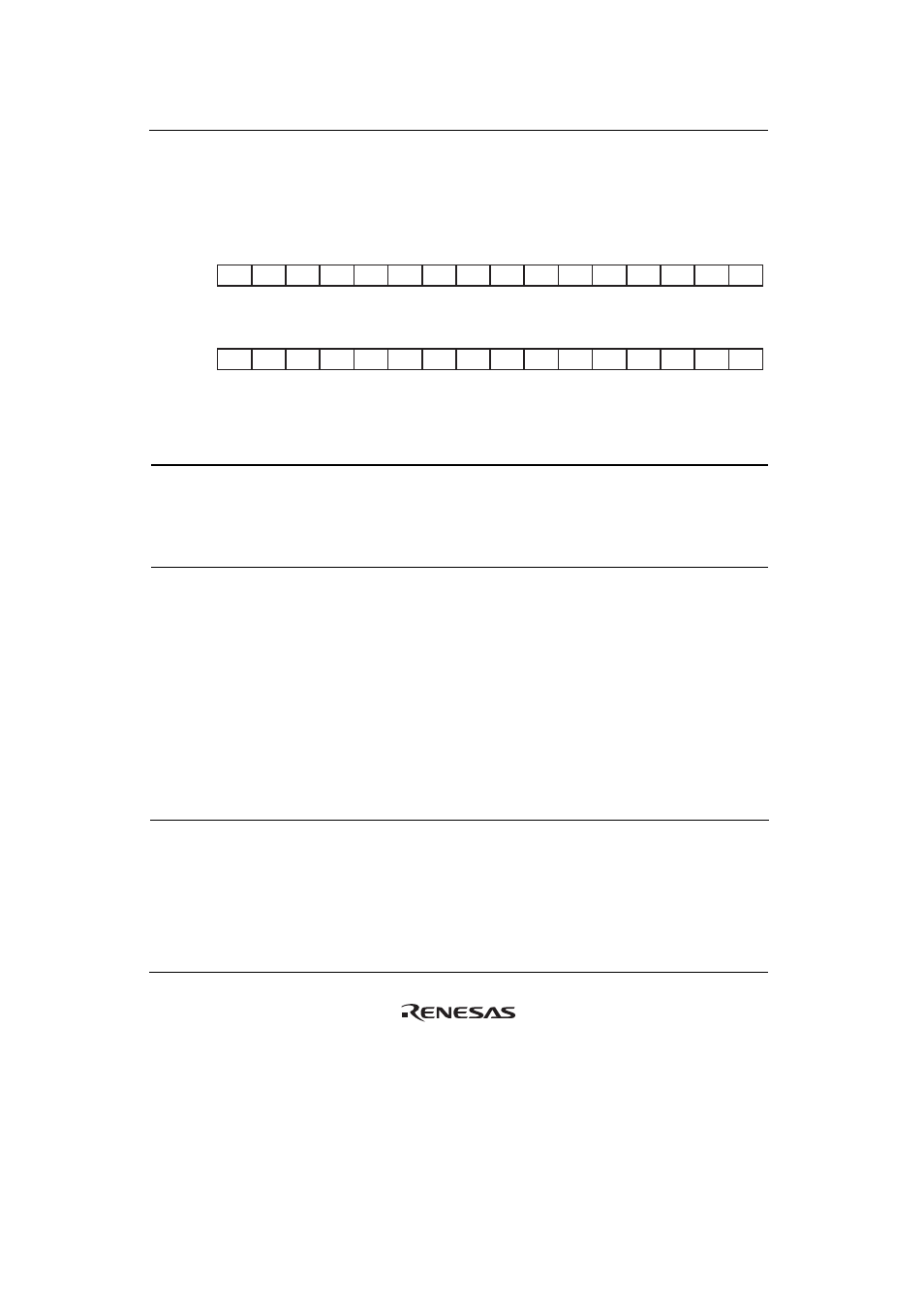

12.4.11

SDRAM Refresh Status Register (DBRFSTS)

The SDRAM refresh status register (DBRFSTS) is a readable/writable register. It is initialized

only upon power-on reset.

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

BIt:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

RFUDF

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

R/W

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

BIt:

Initial value:

R/W:

Bit Bit

Name

Initial

Value R/W

Description

31 to 1

⎯

All 0

R

Reserved

These bits are always read as 0. The write value should

always be 0.

Operation when a value other than 0 is written is not

guaranteed.

0

RFUDF

0

R/W

Refresh Counter Underflow Bit

Set to 1 to indicate that the refresh counter has

underflows when the refresh counter changes from 1 to

0. This bit is cleared to 0 by writing 0 to it.

Underflow may occur because the LV0TH bit value is

smaller than the maximum number of command

execution cycles, so that refresh cannot be issued until

the counter value reaches 0. In this case, the value of

the LV0TH bit should be changed.

For details on the refresh counter, refer to section

12.5.5, Auto-Refresh Operation.

0: Indicates that no underflow occurs.

1: Indicates that an underflow occurs.