6 regarding address multiplexing – Renesas SH7781 User Manual

Page 551

12. DDR2-SDRAM Interface (DBSC2)

Rev.1.00 Jan. 10, 2008 Page 521 of 1658

REJ09B0261-0100

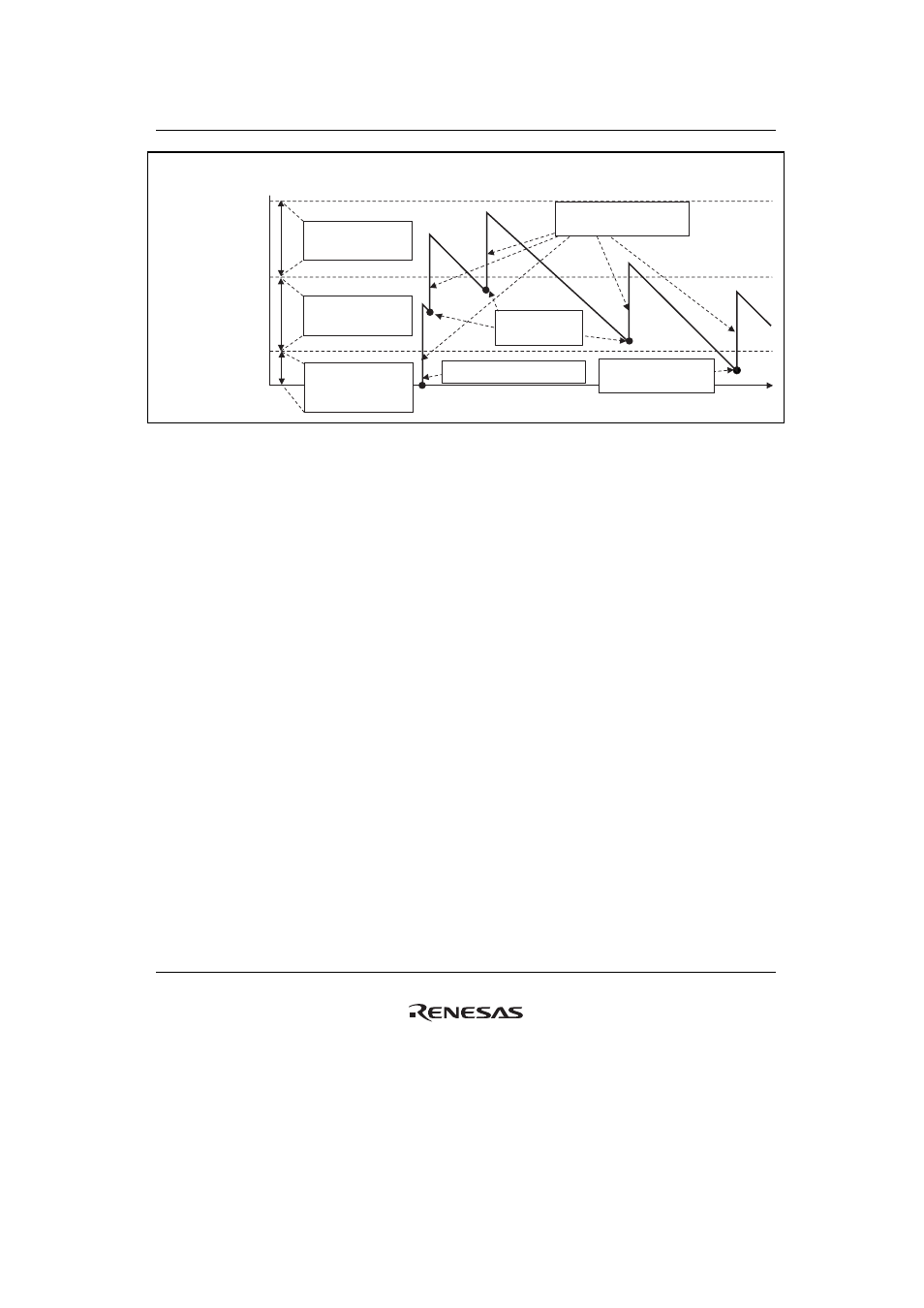

LV1TH

LV0TH

0

Time

Refresh counter

value

Max. value

(Average refresh interval

+ LV1TH)

Level 1

(Refreshing during

request empty cycles)

Level 0

(Refreshing in vacant

periods between

SHwy commands)

Level 2

(Refreshing not done)

Refreshing is done immediately

after auto-refresh is enabled

Refreshing is done in

vacant periods between

SHwy commands

Refreshing is done

during request

empty cycles

The counter value increments

by the amount of

the average refresh interval

Figure 12.7 Relation between Auto-Refresh Operation and Threshold Values

12.5.6

Regarding Address Multiplexing

Memory of various sizes can be connected through the settings of the SDRAM configuration

register (DBCONF). The BWIDTH bits are used to set the external data bus width, and the SPLIT

bit is used to set the size of the memory connected. The BASFT bit setting is used to move the

position of the bank address toward the lower bits; depending on the application the possibility of

page hits may be increased.