3 h-udi reset, Figure 30.4 h-udi reset – Renesas SH7781 User Manual

Page 1536

30. User Debugging Interface (H-UDI)

Rev.1.00 Jan. 10, 2008 Page 1506 of 1658

REJ09B0261-0100

30.4.3

H-UDI Reset

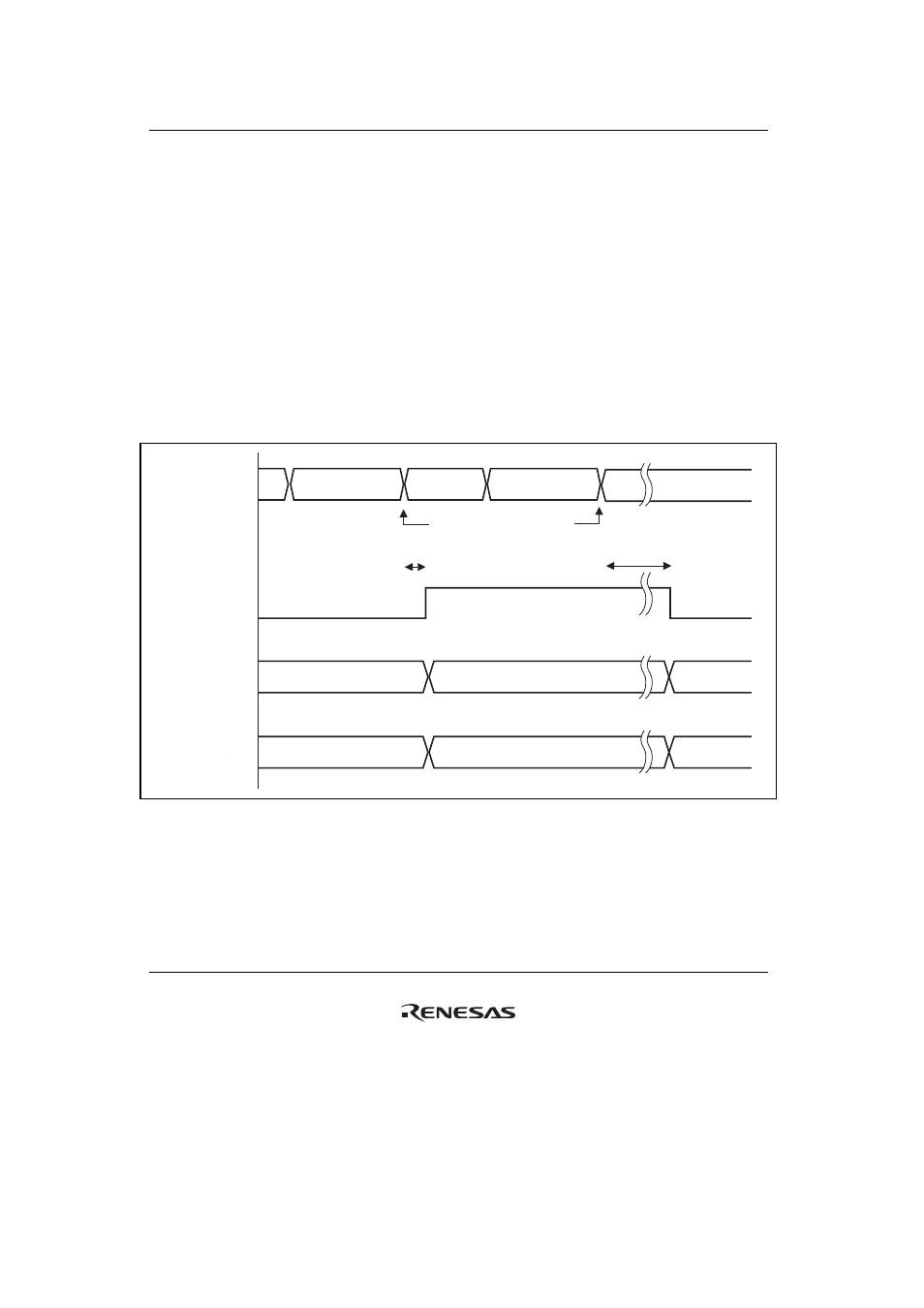

The H-UDI is reset by a power-on reset by the SDIR command. To reset the H-UDI, send the H-

UDI reset assert command from the H-UDI pin, and then send the H-UDI reset negate command

(see figure 30.4). The time required between the H-UDI reset assert and H-UDI reset negate

commands is the same as the time to keep the reset pin low in order to reset this LSI by a power-

on reset. After the H-UDI reset assert command is set, the reset signal is asserted in the chip after

four cycles at a peripheral clock (Pck). When the H-UDI reset negate command is set, the reset

signal is negated in the chip after a reset hold period. (The minimum period is 17 cycles at a

peripheral clock, and the maximum period is 42 cycles at a peripheral clock. For details, see

section 15, Clock Pulse Generator (CPG).)

Note: The WDT/RST module is not initialized. However, the overflow counter of the WDT/RST

module is initialized.

Reset in the chip

H-UDI

reset asserted

H-UDI

reset negated

H-UDI pin

Command set timing

Pck 4 cycles

Reset hold period

Reset

Normal

Reset processing

CPU state

STATUS[1:0] output

LL (normal)

HH (reset)

LL (normal)

Figure 30.4 H-UDI Reset