Renesas SH7781 User Manual

Page 187

7. Memory Management Unit (MMU)

Rev.1.00 Jan. 10, 2008 Page 157 of 1658

REJ09B0261-0100

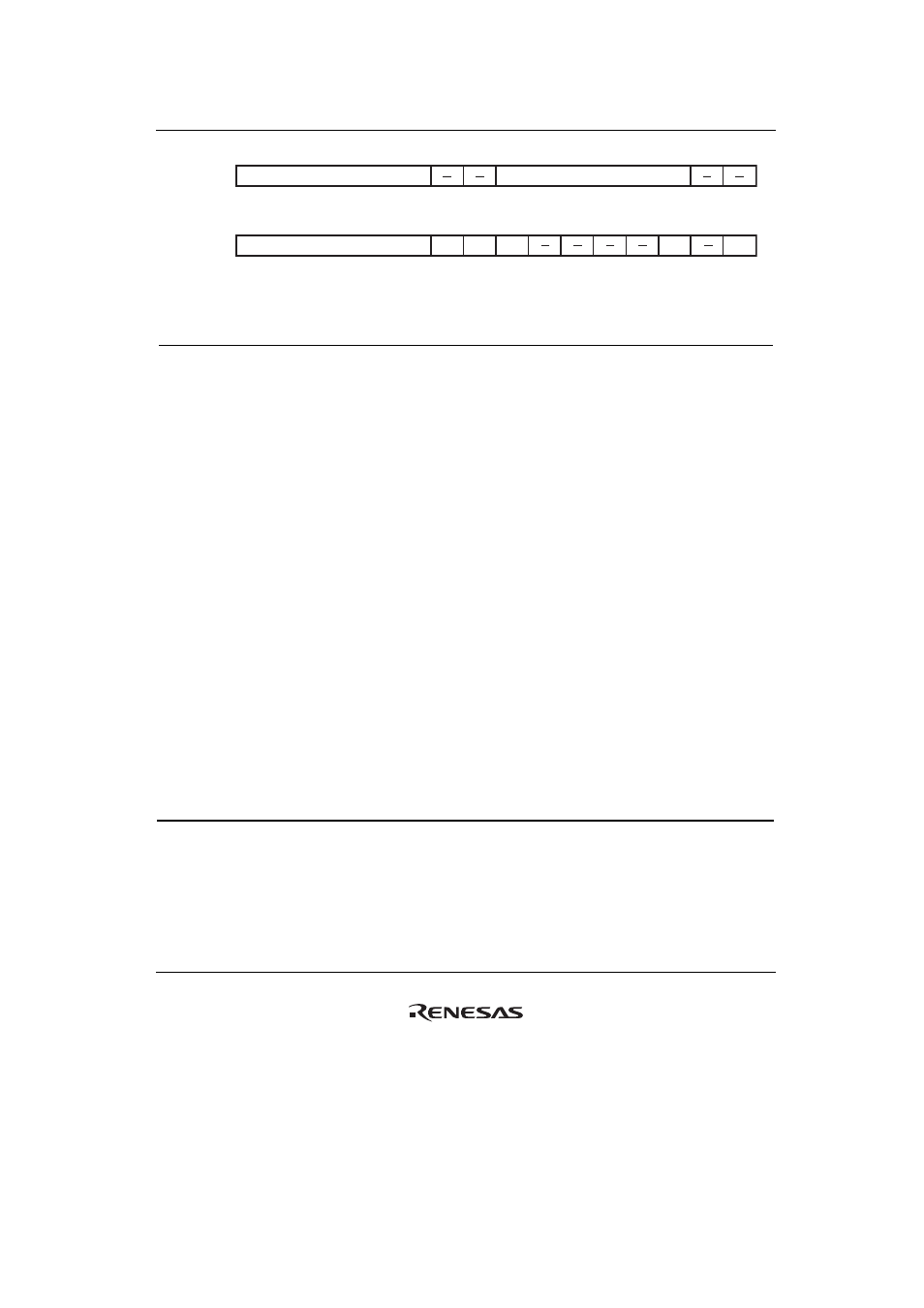

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Bit:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Initial value:

R/W

R/W

R/W

R/W

R/W

R/W

R

R

R/W

R/W

R/W

R/W

R/W

R/W

R

R

R/W

R

R

TI

URB

LRUI

URC

SQMD SV

AT

R

R

R/W

R

R/W

R/W:

Bit:

Initial value:

R/W:

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

ME

Bit Bit

Name

Initial

Value R/W Description

31 to 26 LRUI

000000

R/W

Least Recently Used ITLB

These bits indicate the ITLB entry to be replaced. The

LRU (least recently used) method is used to decide the

ITLB entry to be replaced in the event of an ITLB miss.

The entry to be purged from the ITLB can be confirmed

using the LRUI bits.

LRUI is updated by means of the algorithm shown below.

x means that updating is not performed.

000xxx: ITLB entry 0 is used

1xx00x: ITLB entry 1 is used

x1x1x0: ITLB entry 2 is used

xx1x11: ITLB entry 3 is used

xxxxxx: Other than above

When the LRUI bit settings are as shown below, the

corresponding ITLB entry is updated by an ITLB miss.

Ensure that values for which "Setting prohibited" is

indicated below are not set at the discretion of software.

After a power-on or manual reset, the LRUI bits are

initialized to 0, and therefore a prohibited setting is never

made by a hardware update.

x means "don't care".

111xxx: ITLB entry 0 is updated

0xx11x: ITLB entry 1 is updated

x0x0x1: ITLB entry 2 is updated

xx0x00: ITLB entry 3 is updated

Other than above: Setting prohibited