Renesas SH7781 User Manual

Page 702

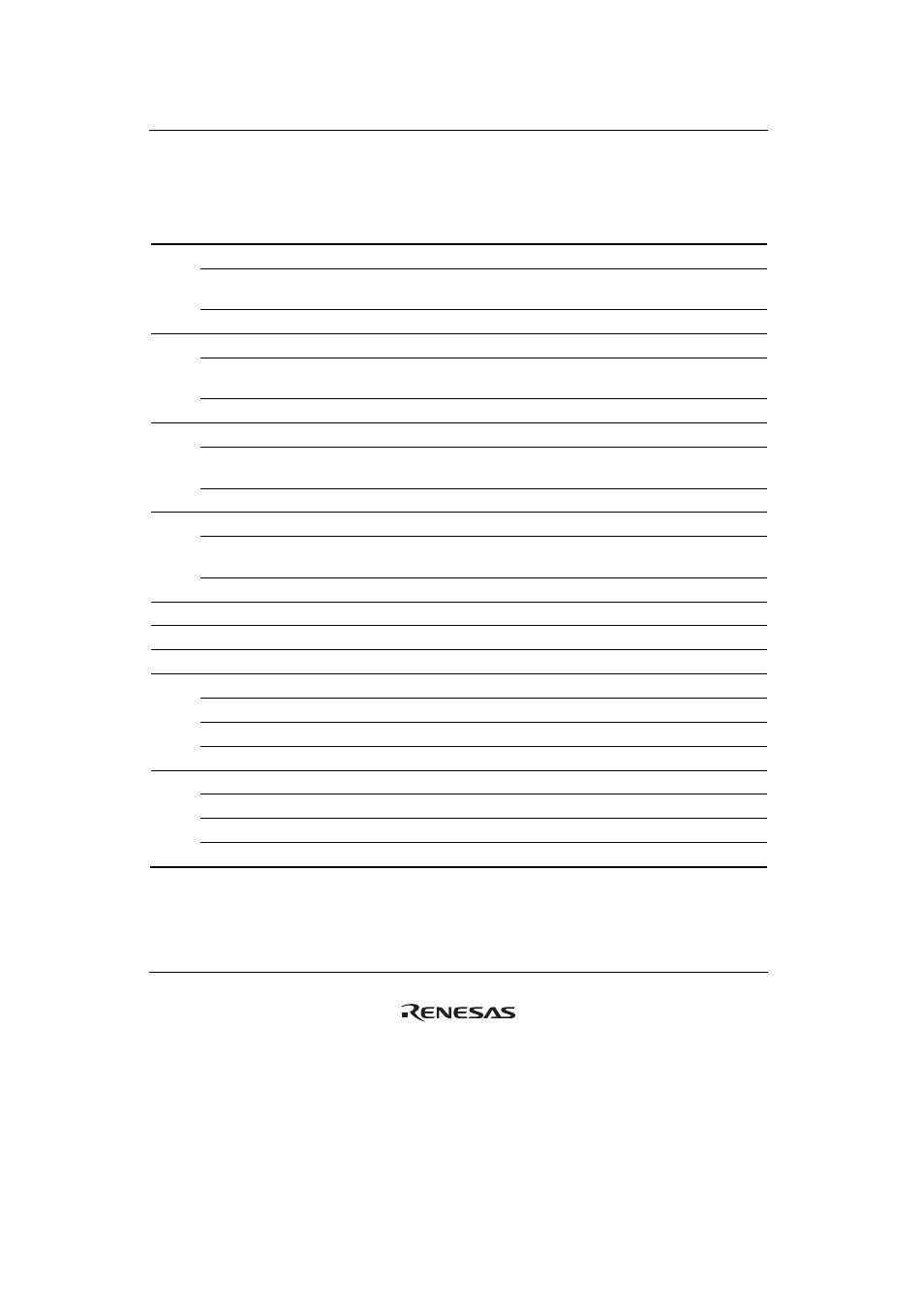

14. Direct Memory Access Controller (DMAC)

Rev.1.00 Jan. 10, 2008 Page 672 of 1658

REJ09B0261-0100

Channel Name

Abbrev.

Power-on

Reset

by

PRESET

Pin/WDT/

H-UDI

Manual

Reset

by

WDT/Multiple

Exception

Sleep

by SLEEP

instruction

Deep Sleep

by SLEEP

instruction

(DSLP = 1)

Module

Standby

0

DMA source address register B0

SARB0

Undefined

Undefined

Retained

Retained

Retained

DMA destination address register

B0

DARB0 Undefined Undefined Retained Retained Retained

DMA transfer count register B0

TCRB0

Undefined

Undefined

Retained

Retained

Retained

1

DMA source address register B1

SARB1

Undefined

Undefined

Retained

Retained

Retained

DMA destination address register

B1

DARB1 Undefined Undefined Retained Retained Retained

DMA transfer count register B1

TCRB1

Undefined

Undefined

Retained

Retained

Retained

2

DMA source address register B2

SARB2

Undefined

Undefined

Retained

Retained

Retained

DMA destination address register

B2

DARB2 Undefined Undefined Retained Retained Retained

DMA transfer count register B2

TCRB2

Undefined

Undefined

Retained

Retained

Retained

3

DMA source address register B3

SARB3

Undefined

Undefined

Retained

Retained

Retained

DMA destination address register

B3

DARB3 Undefined Undefined Retained Retained Retained

DMA transfer count register B3

TCRB3

Undefined

Undefined

Retained

Retained

Retained

0, 1

DMA extended resource selector 0

DMARS0 H'0000

H'0000

Retained

Retained

Retained

2, 3

DMA extended resource selector 1

DMARS1 H'0000

H'0000

Retained

Retained

Retained

4, 5

DMA extended resource selector 2

DMARS2 H'0000

H'0000

Retained

Retained

Retained

6

DMA source address register 6

SAR6

Undefined

Undefined

Retained

Retained

Retained

DMA destination address register 6 DAR6

Undefined

Undefined

Retained

Retained

Retained

DMA transfer count register 6

TCR6

Undefined

Undefined

Retained

Retained

Retained

DMA channel control register 6

CHCR6

H'4000 0000 H'4000 0000

Retained

Retained

Retained

7

DMA source address register 7

SAR7

Undefined

Undefined

Retained

Retained

Retained

DMA destination address register 7 DAR7

Undefined

Undefined

Retained

Retained

Retained

DMA transfer count register 7

TCR7

Undefined

Undefined

Retained

Retained

Retained

DMA channel control register 7

CHCR7

H'4000 0000 H'4000 0000

Retained

Retained

Retained