7 sdram timing register 2 (dbtr2) – Renesas SH7781 User Manual

Page 525

12. DDR2-SDRAM Interface (DBSC2)

Rev.1.00 Jan. 10, 2008 Page 495 of 1658

REJ09B0261-0100

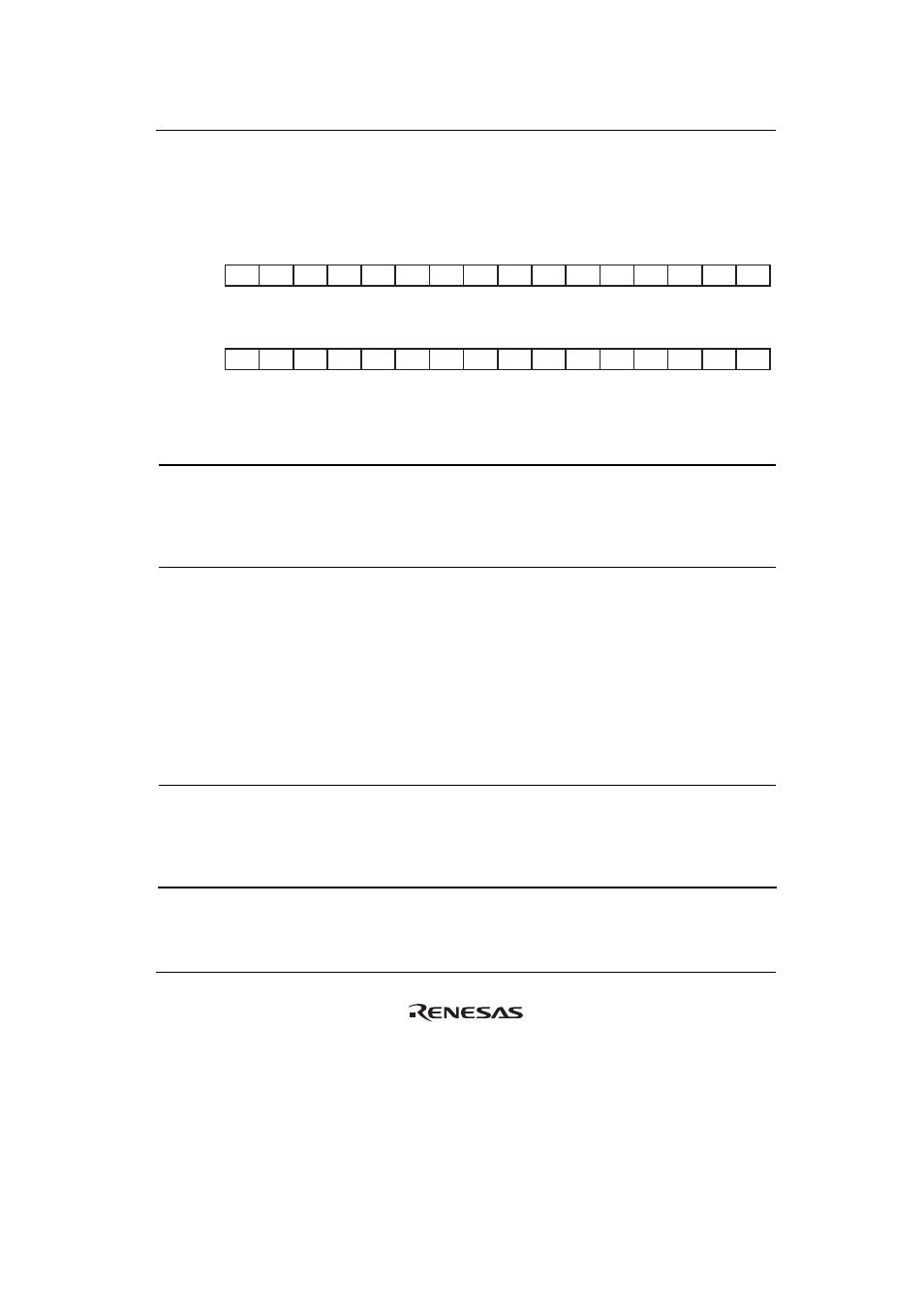

12.4.7

SDRAM Timing Register 2 (DBTR2)

The SDRAM timing register 2 (DBTR2) is a readable/writable register. It is initialized only upon

power-on reset.

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

0

0

1

0

0

0

0

0

1

0

0

0

0

0

0

0

TRC0

TRC1

TRC2

TRC3

TRC4

⎯

⎯

⎯

TRTP0

TRTP1

⎯

⎯

⎯

⎯

⎯

⎯

R/W

R/W

R/W

R/W

R/W

R

R

R

R/W

R/W

R

R

R

R

R

R

BIt:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

1

1

0

0

0

0

0

0

1

1

0

0

0

0

0

0

WRRD0

WRRD1

WRRD2

WRRD3

⎯

⎯

⎯

⎯

RDWR0

RDWR1

RDWR2

RDWR3

⎯

⎯

⎯

⎯

R/W

R/W

R/W

R/W

R

R

R

R

R/W

R/W

R/W

R/W

R

R

R

R

BIt:

Initial value:

R/W:

Bit Bit

Name

Initial

Value R/W

Description

31 to 26

⎯

All 0

R

Reserved

These bits are always read as 0. The write value should

always be 0.

Operation when a value other than 0 is written is not

guaranteed.

25, 24

TRTP1 and

TRTP0

01

R/W

tRTP (READ-PRE command minimum time) Setting Bits

These bits set the READ-PRE command minimum time

constraint for the same bank. These bits should be set

according to the SDRAM specifications. The number of

cycles is the number of DDR clock cycles.

00: Setting prohibit (If specified, correct operation

cannot be guaranteed.)

01: 2 cycles

10: 3 cycles

11: Setting prohibit (If specified, correct operation

cannot be guaranteed.)

23 to 21

⎯

All 0

R

Reserved

These bits are always read as 0. The write value should

always be 0.

Operation when a value other than 0 is written is not

guaranteed.