Renesas SH7781 User Manual

Page 295

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 265 of 1658

REJ09B0261-0100

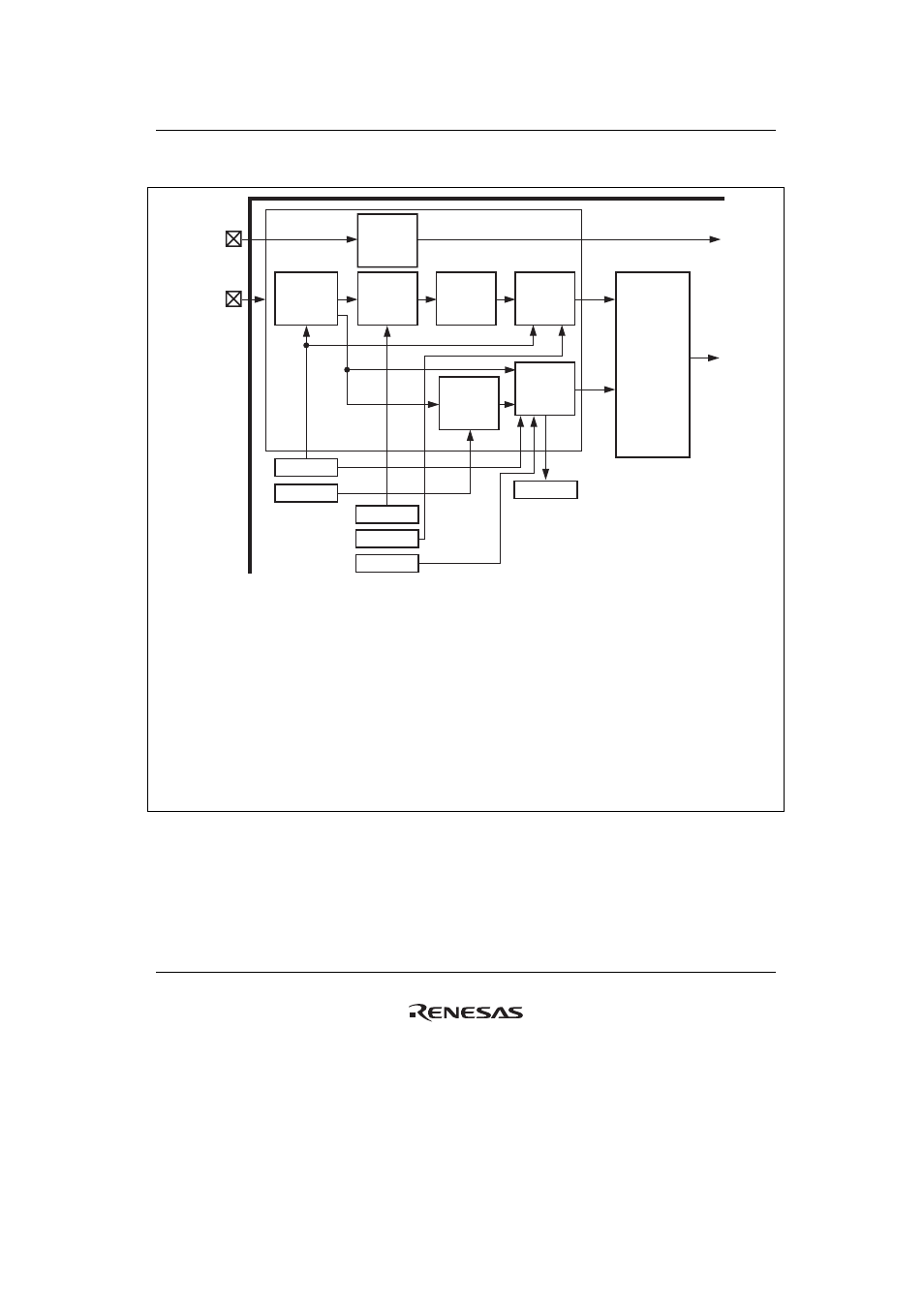

The details of the input control circuit of figure 10.1 are shown in figure 10.2.

NMI

IRQ/

IRL7 to

IRQ/

IRL0

NMI

detector*

4

Input control

NMI interrupt

request

INTC

IRL

mask

controller

Noise

canceller

Noise

canceller

for level

detection

IRL

detector*

2

Priority

determination

for external

interrupts

IRQ

detector*

3

IRL/IRQ

pin mode

controller*

1

ICR0

ICR1

INTMSK2

INTREQ

INTMSK1

INTMSK0

IRL

IRQ

Notes: 1. The internal signal for IRQ is fixed when ICR0.IRLMn (n = 0, 1) is cleared to 0, and the

internal signal for IRL is fixed when ICR0.IRLMn is set to 1 to prevent propagation of the state

transition on the pin to inside the LSI.

2. IRL detector includes a noise canceller.

When the interrupt source holding mode bit (ICR0.LVLMODE) is cleared to 0, the interrupt

source bits for the detected IRL interrupt request are retained in the INTC. When

ICR0.LVLMODE = 1, the interrupt source bits are not retained.

In the case of ICR0.LVLMODE = 0, if the IRL interrupt request masking is set by INTMSK2

after the interrupt source bit is retained, the IRL interrupt request of the source that has

already been retained will not be masked. To clear the retained interrupt request, refer to

section 10.7.1.

3. When the IRQ interrupt is configured for level-sense, the interrupt source bit of the IRQ

interrupt detected by this circuit is retained if ICR0.LVLMODE = 0. The interrupt source bits of

the level-sense IRQ are not retained if ICR0.LVLMODE = 1.

4. This circuit detects the NMI interrupt request.

Figure 10.2 Input Control Circuit for the Interrupt Requested from the External Pin