Renesas SH7781 User Manual

Page 1664

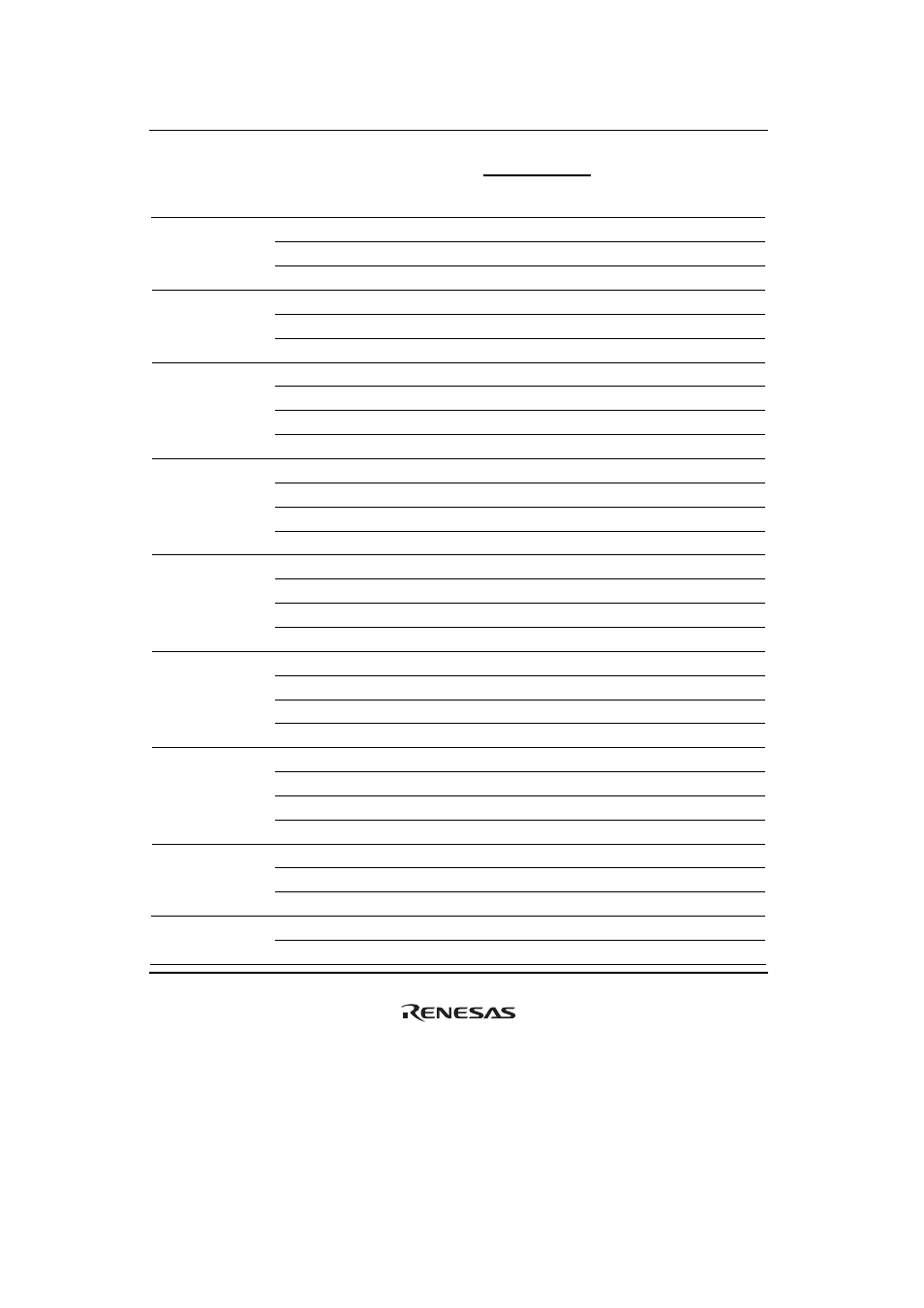

Appendix

Rev.1.00 Jan. 10, 2008 Page 1634 of 1658

REJ09B0261-0100

Reset

Pin Name

(LSI level)

Pin Name

(Module level)

Related

Module I/O

Power

-on Manual Sleep

Module

Standby

Bus

Release

AD[31:24] PCIC I/O

PZ K K

⎯

K

D[63:56] LBSC

I/O

PZ

K K

⎯

Z

D[63:56]/

AD[31:24]

*

3

Port A[7:0]

GPIO

I/O

PZ

K

K

⎯

K

AD[23:18] PCIC I/O

PZ K K

⎯

K

D[55:50] LBSC

I/O

PZ

K K

⎯

Z

D[55:50]/

AD[23:18]

*

3

Port B[7:2]

GPIO

I/O

PZ

K

K

⎯

K

AD[17:16] PCIC I/O

PZ K K

⎯

K

D[49:48] LBSC

I/O

PZ

K K

⎯

Z

DB[5:4] DU O

PZ

K

K

K K

D[49:48]/

AD[17:16]/

DB[5:4]

*

3

Port B[1:0]

GPIO

I/O

⎯

K K

⎯

K

AD[15:12] PCIC I/O

PZ K K

⎯

K

D[47:44] LBSC

I/O

PZ

K K

⎯

Z

DB[3:0] DU O

PZ

K

K

K K

D[47:44]/

AD[15:12]/

DB[3:0]

*

3

Port C[7:4]

GPIO

I/O

⎯

K K

⎯

K

AD[11:8] PCIC

I/O

PZ

K K

⎯

K

D[43:40] LBSC

I/O

PZ

K K

⎯

Z

DG[5:2] DU O

PZ

K

K

K K

D[43:40]/

AD[11:8]/

DG[5:2]

*

3

Port C[3:0]

GPIO

I/O

⎯

K K

⎯

K

AD[7:6] PCIC

I/O

PZ

K

K

⎯

K

D[39:38] LBSC

I/O

PZ

K K

⎯

Z

DG[1:0] DU O

PZ

K

K

K K

D[39:38]/

AD [7:6]/

DG[1:0]

*

3

Port D[7:6]

GPIO

I/O

⎯

K K

⎯

K

AD[5:0] PCIC

I/O

PZ

K

K

⎯

K

D[37:32] LBSC

I/O

PZ

K K

⎯

Z

DR[5:0] DU O

PZ

K

K

K K

D[37:32]/

AD[5:0]/

DR[5:0]

*

3

Port D[5:0]

GPIO

I/O

⎯

K K

⎯

K

CBE[3:0] PCIC

I/O

PZ

K K

⎯

K

WE[7:4] LBSC

O

PZ

K

K

⎯

Z

WE[7:4]/

CBE [3:0]

*

3

Port R[3:0]

GPIO

I/O

PZ

K

K

⎯

K

GNT0/GNTIN*

3

GNT0/GNTIN PCIC

I/O PZ

K

K

⎯

K

Port Q3

GPIO

I/O

PZ

K

K

⎯

K