2 transition to 32-bit address extended mode – Renesas SH7781 User Manual

Page 230

7. Memory Management Unit (MMU)

Rev.1.00 Jan. 10, 2008 Page 200 of 1658

REJ09B0261-0100

7.8.2

Transition to 32-Bit Address Extended Mode

This LSI enters 29-bit address mode after a power-on reset. Transition is made to 32-bit address

extended mode by setting the SE bit in PASCR to 1. In 32-bit address extended mode, the MMU

operates as follows.

1. When the AT bit in MMUCR is 0, virtual addresses in the U0, P0, or P3 area become 32-bit

physical addresses. Addresses in the P1 or P2 area are translated according to the PMB

mapping information. B'10 should be set to the upper 2 bits of virtual page number

(VPN[31:30]) in the PMB in order to indicate P1 or P2 area. The operation is not guaranteed

when the value except B'10 is set to these bits.

2. When the AT bit in MMUCR is 1, virtual addresses in the U0, P0, or P3 area are translated to

32-bit physical addresses according to the TLB conversion information. Addresses in the P1 or

P2 area are translated according to the PMB mapping information. B'10 should be set to the

upper 2 bits of virtual page number (VPN[31:30]) in the PMB in order to indicate P1 or P2

area. The operation is not guaranteed when the value except B'10 is set to these bits.

3. Regardless of the setting of the AT bit in MMUCR, bits 31 to 29 in physical addresses become

B'111 in the control register area (addresses H'FC00 0000 to H'FFFF FFFF). When the control

register area is recorded in the UTLB and accessed, B'111 should be set to PPN[31:29].

7.8.3

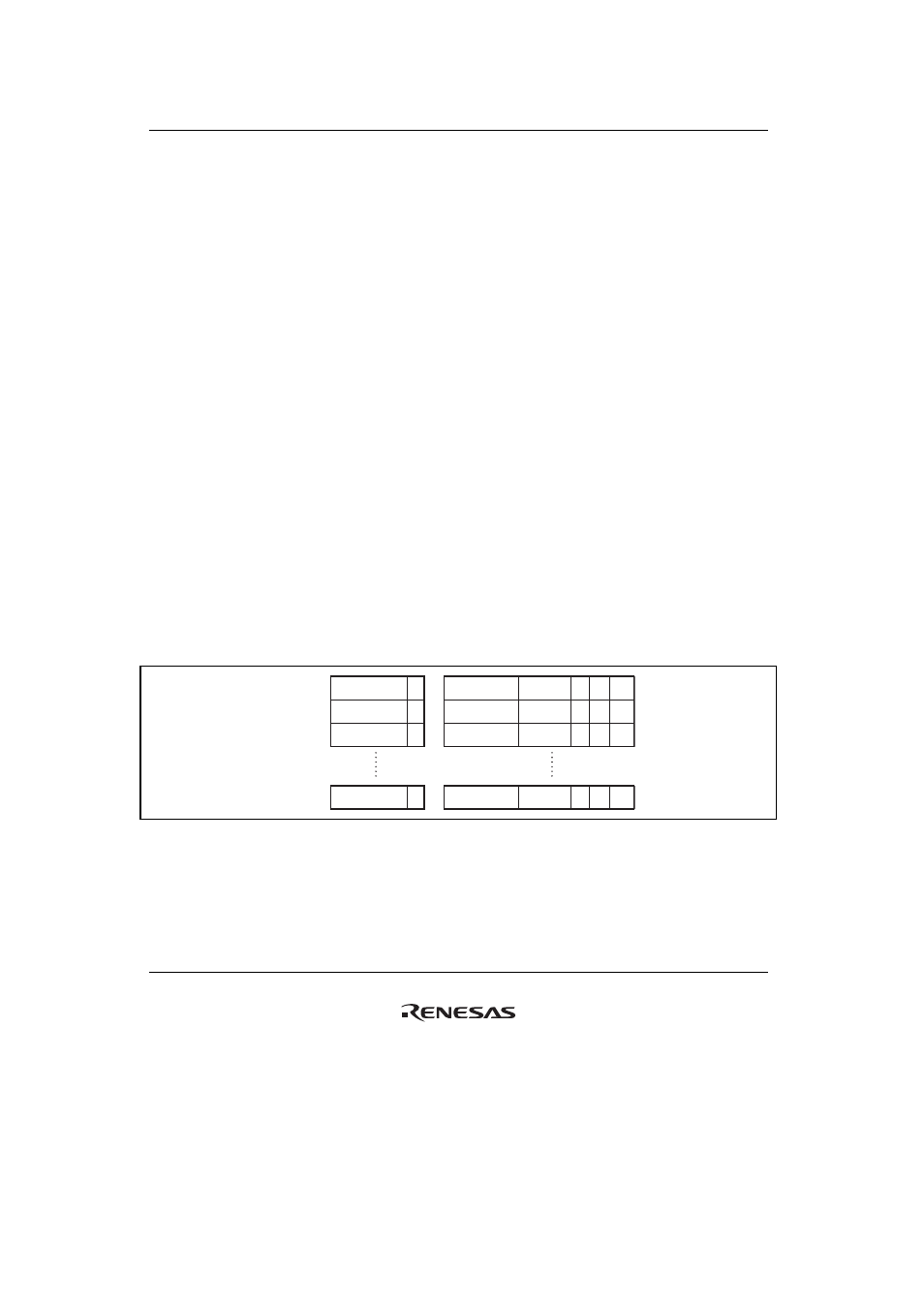

Privileged Space Mapping Buffer (PMB) Configuration

In 32-bit address extended mode, virtual addresses in the P1 or P2 area are translated according to

the PMB mapping information. The PMB has 16 entries and configuration of each entry is as

follows.

PPN[31:24]

PPN[31:24]

PPN[31:24]

SZ[1:0]

SZ[1:0]

SZ[1:0]

C

C

C

UB

UB

UB

VPN[31:24]

VPN[31:24]

VPN[31:24]

V

V

V

Entry 0

Entry 1

Entry 2

WT

WT

WT

PPN[31:24]

SZ[1:0]

C UB

VPN[31:24]

V

Entry 15

WT

Figure 7.27 PMB Configuration