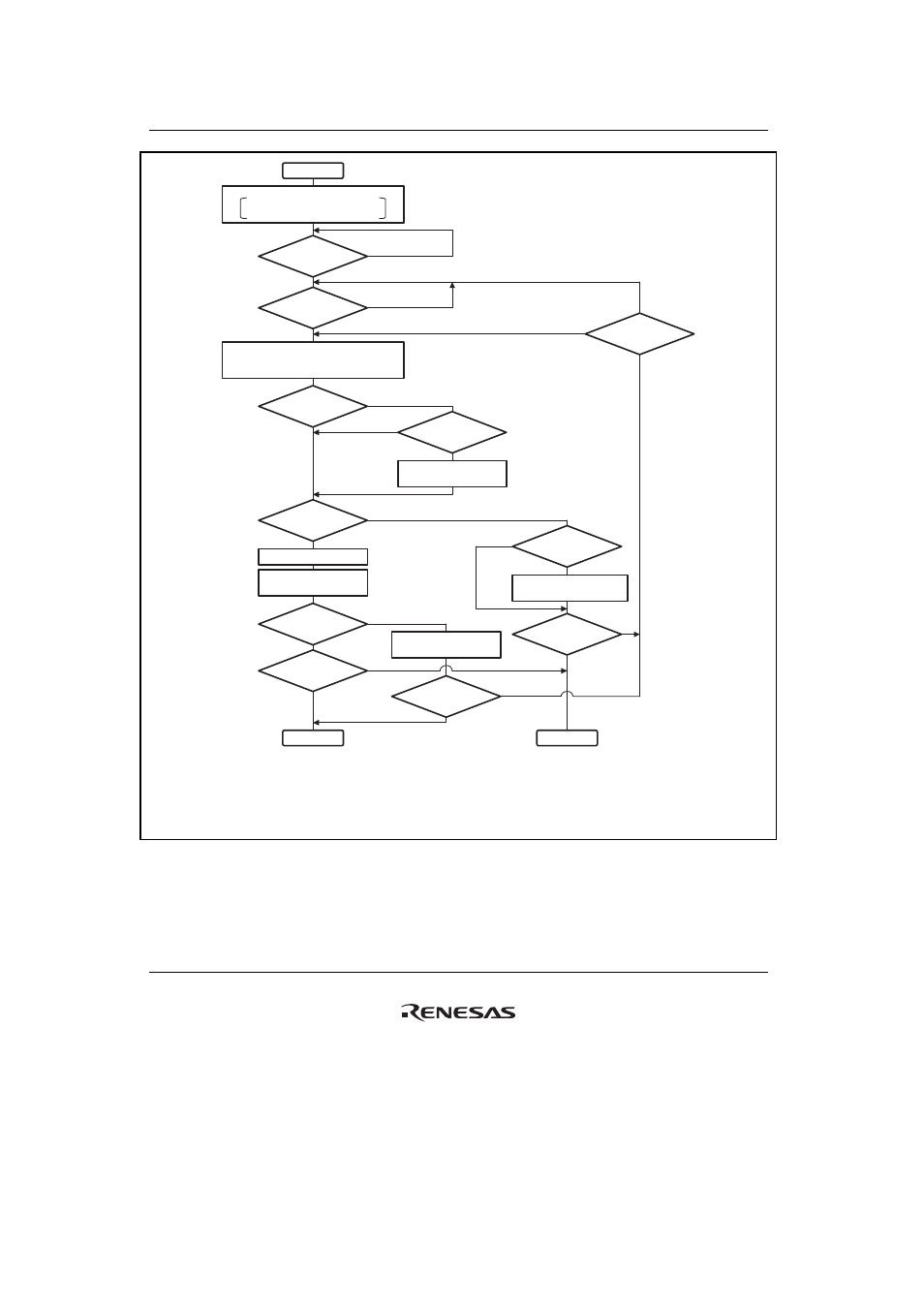

Figure 14.11 flowchart of dma transfer – Renesas SH7781 User Manual

Page 748

14. Direct Memory Access Controller (DMAC)

Rev.1.00 Jan. 10, 2008 Page 718 of 1658

REJ09B0261-0100

Notes: 1. In repeat mode, a transfer request is acceptted with TE =1 when HIE = 1 and HE = 0

(half end interrupt is enable and clear the HE to 0 after HE is set to 1).

2. In auto-request mode, transfer starts when bits NMIF, AE, and TE are all 0 or bits TE

and HIE are 1 and HE is 0 (in repeat mode), and bits DE and DME are set to 1.

3. DREQ is level detection (external request) in burst mode or cycle-steral mode.

4. DREQ is edge detection (external request) or auto request in burst mode.

5. Loading to SAR and DAR differs according to the operating conditions in each mode.

6. TCRBH and TCRBL refer to TCRB23 to TCRB16 and TCRB7 to TCRB0 respectively.

NMIF = 1 or AE =1 or

DE = 0 or DME = 0?

Normal end

Transfer end

NMIF = 1 or AE = 1 or

DE = 0 or DME = 0?

SARB/DARB load

TCRB

→ TCR load

HIE = 0 or HE = 1?

Yes

Yes

No

No

*

5

No

Yes

TCR = 0?

TE = 1

DMINT interrupt request

(IE = 1)

Repeat mode?

TCR = TCRB/2?

HE = 1, DMINT interrupt

request (HIE = 1)

Yes

Yes

Yes

No

No

No

Transfer (1 transfer unit);

TCR – 1

→ TCR, SAR, and DAR updated

Reload mode: TCRBL – 1

→ TCRBL

Reload mode?

TCRBL = 0?

SARB/DARB load

TCRBH

→ TCRBL load

Bus mode, DREQ

detection system,

transfer request mode

Yes

No

*

5

Yes

No

*

6

*

6

Start

Initial settings

SAR, DAR, TCR, CHCR, DMAOR

SARB, DARB, TCRB, DMARS

DE, DME = 1 and

TE, AE, NMIF = 0?

Transfer request occurs?

No

No

*

1

*

2

*

3

*

4

Yes

Yes

Figure 14.11 Flowchart of DMA Transfer