Renesas SH7781 User Manual

Page 90

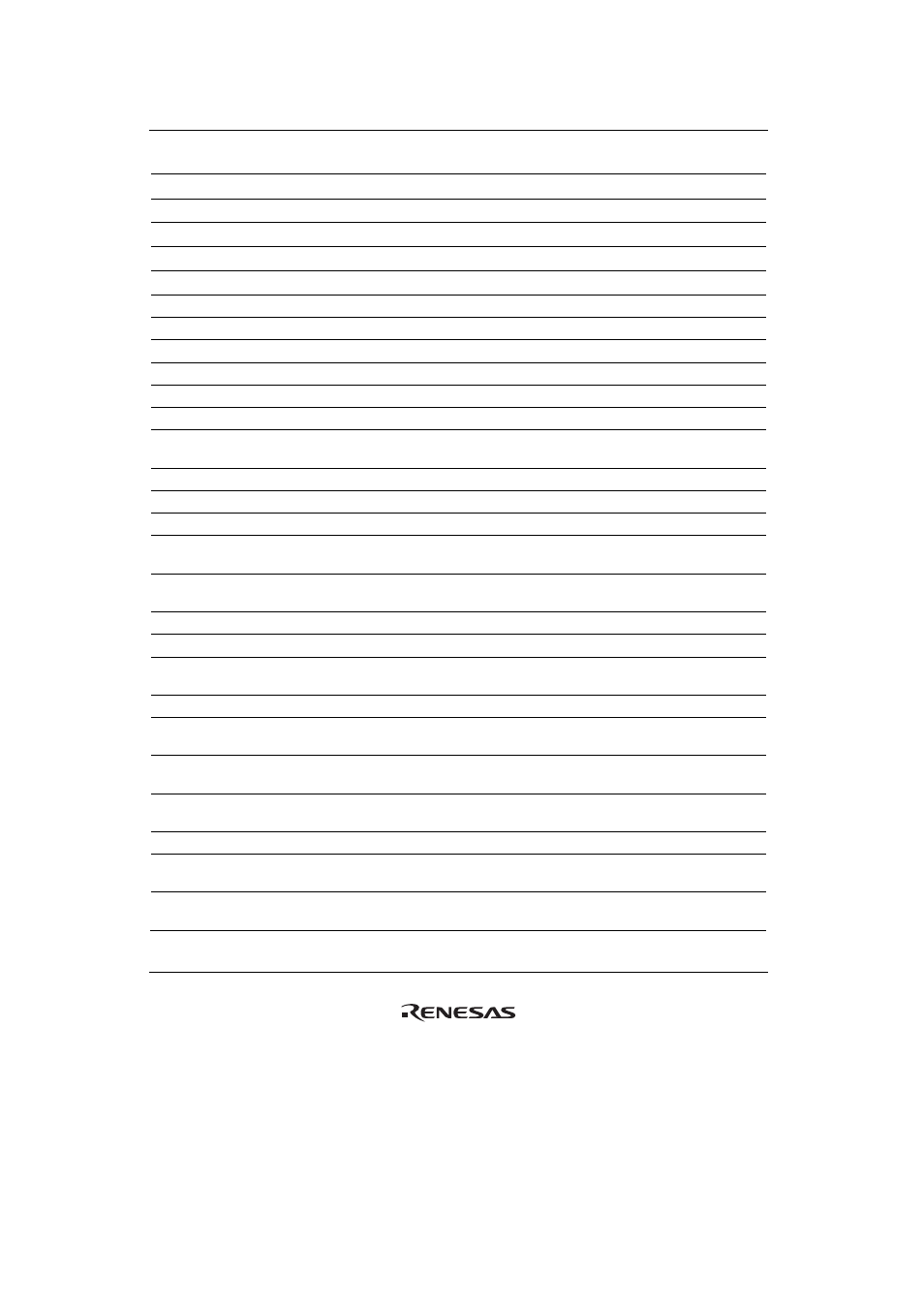

3. Instruction Set

Rev.1.00 Jan. 10, 2008 Page 60 of 1658

REJ09B0261-0100

Instruction Operation

Instruction Code

Privileged T Bit New

LDC Rm,SSR Rm

→ SSR

0100mmmm00111110 Privileged —

—

LDC Rm,SPC Rm

→ SPC

0100mmmm01001110 Privileged —

—

LDC Rm,DBR Rm

→ DBR

0100mmmm11111010 Privileged —

—

LDC Rm,Rn_BANK

Rm

→ Rn_BANK (n = 0 to 7) 0100mmmm1nnn1110 Privileged — —

LDC.L @Rm+,SR (Rm)

→ SR, Rm + 4 → Rm 0100mmmm00000111 Privileged LSB —

LDC.L @Rm+,GBR

(Rm)

→ GBR, Rm + 4 → Rm 0100mmmm00010111 — —

—

LDC.L @Rm+,VBR

(Rm)

→ VBR, Rm + 4 → Rm 0100mmmm00100111 Privileged — —

LDC.L @Rm+,SGR

(Rm)

→ SGR, Rm + 4 → Rm 0100mmmm00110110 Privileged — —

LDC.L @Rm+,SSR

(Rm)

→ SSR, Rm + 4 → Rm 0100mmmm00110111 Privileged — —

LDC.L @Rm+,SPC

(Rm)

→ SPC, Rm + 4 → Rm 0100mmmm01000111 Privileged — —

LDC.L @Rm+,DBR

(Rm)

→ DBR, Rm + 4 → Rm 0100mmmm11110110 Privileged — —

LDC.L @Rm+,Rn_

BANK

(Rm)

→ Rn_BANK,

Rm + 4

→ Rm

0100mmmm1nnn0111

Privileged — —

LDS Rm,MACH

Rm

→ MACH

0100mmmm00001010

— —

—

LDS Rm,MACL

Rm

→ MACL

0100mmmm00011010

— —

—

LDS Rm,PR Rm

→ PR

0100mmmm00101010

— —

—

LDS.L @Rm+,MACH

(Rm)

→ MACH, Rm + 4 →

Rm

0100mmmm00000110

— —

—

LDS.L @Rm+,MACL

(Rm)

→ MACL, Rm + 4 →

Rm

0100mmmm00010110

— —

—

LDS.L @Rm+,PR (Rm)

→ PR, Rm + 4 → Rm 0100mmmm00100110 — —

—

LDTLB

PTEH/PTEL

(/PTEA)

→ TLB 0000000000111000 Privileged — —

MOVCA.L R0,@Rn

R0

→ (Rn) (without fetching

cache block)

0000nnnn11000011

— —

—

NOP

No

operation

0000000000001001

— —

—

OCBI

@Rn

Invalidates operand cache

block

0000nnnn10010011

— —

—

OCBP

@Rn

Writes back and invalidates

operand cache block

0000nnnn10100011

— —

—

OCBWB

@Rn

Writes back operand cache

block

0000nnnn10110011

— —

—

PREF @Rn

(Rn)

→ operand cache

0000nnnn10000011

— —

—

PREFI @Rn

Reads

32-byte

instruction

block into instruction cache

0000nnnn11010011

⎯

⎯ New

RTE

Delayed

branch,

SSR/SPC

→ SR/PC

0000000000101011

Privileged — —