Renesas SH7781 User Manual

Page 699

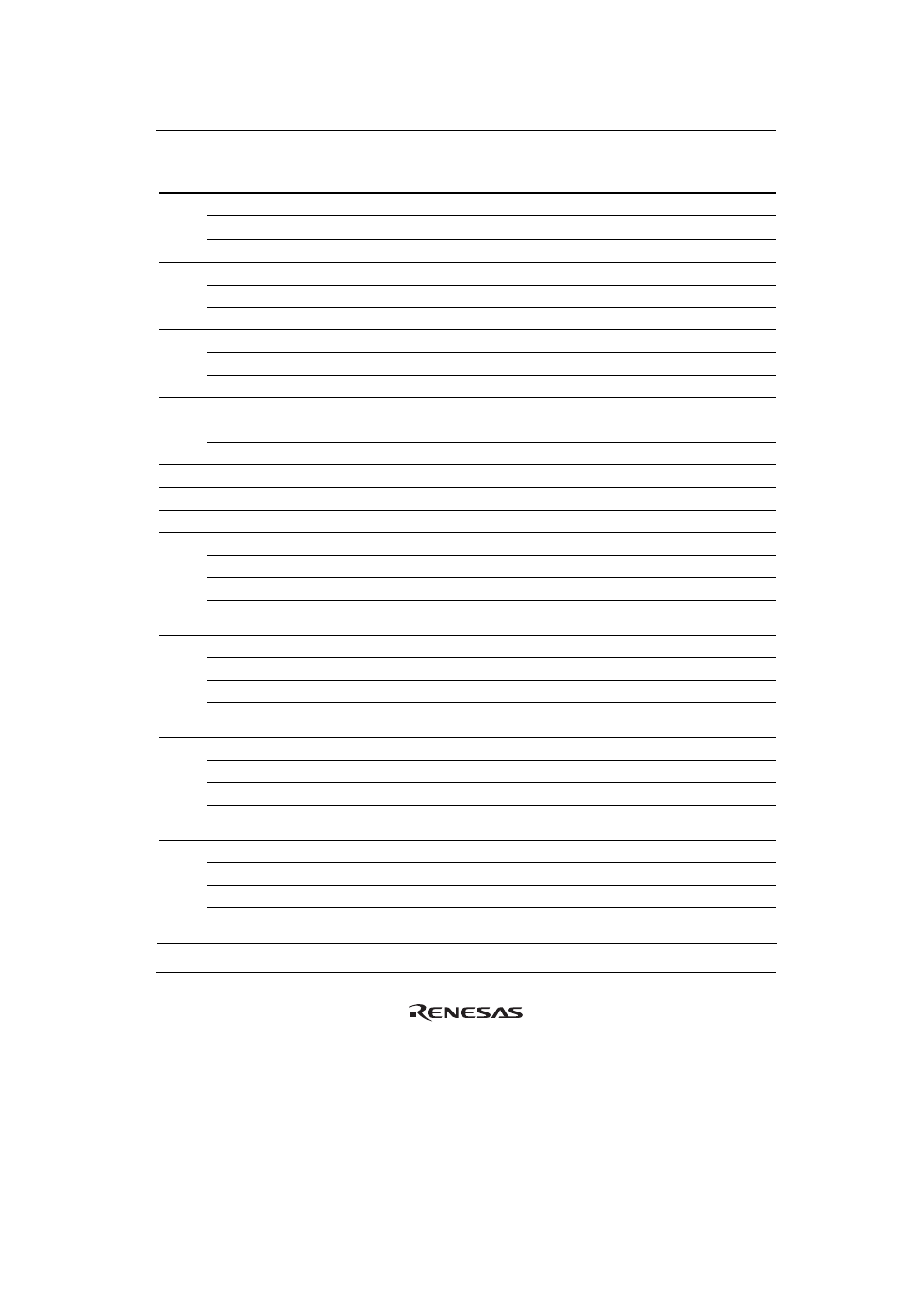

14. Direct Memory Access Controller (DMAC)

Rev.1.00 Jan. 10, 2008 Page 669 of 1658

REJ09B0261-0100

Channel Name

Abbrev. R/W P4

Address

Area 7

Address

Access

Size*

3

Sync

clock

0

DMA source address register B0

SARB0 R/W H'FC80

8120

H'1C80

8120 32 Bck

DMA destination address register B0 DARB0 R/W H'FC80

8124 H'1C80

8124 32

Bck

DMA transfer count register B0

TCRB0

R/W

H'FC80 8128

H'1C80 8128

32

Bck

1

DMA source address register B1

SARB1 R/W H'FC80

8130

H'1C80

8130 32 Bck

DMA destination address register B1 DARB1 R/W H'FC80

8134 H'1C80

8134 32

Bck

DMA transfer count register B1

TCRB1

R/W

H'FC80 8138

H'1C80 8138

32

Bck

2

DMA source address register B2

SARB2 R/W H'FC80

8140

H'1C80

8140 32 Bck

DMA destination address register B2 DARB2 R/W H'FC80

8144 H'1C80

8144 32

Bck

DMA transfer count register B2

TCRB2

R/W

H'FC80 8148

H'1C80 8148

32

Bck

3

DMA source address register B3

SARB3 R/W H'FC80

8150

H'1C80

8150 32 Bck

DMA destination address register B3 DARB3 R/W H'FC80

8154 H'1C80

8154 32

Bck

DMA transfer count register B3

TCRB3

R/W

H'FC80 8158

H'1C80 8158

32

Bck

0, 1

DMA extended resource selector 0 DMARS0 R/W H'FC80

9000 H'1C80

9000 16

Pck

2, 3

DMA extended resource selector 1 DMARS1 R/W H'FC80

9004 H'1C80

9004 16

Pck

4, 5

DMA extended resource selector 2 DMARS2 R/W H'FC80

9008 H'1C80

9008 16

Pck

6

DMA source address register 6

SAR6 R/W

H'FCC0

8020

H'1CC0

8020

32 Bck

DMA destination address register 6

DAR6 R/W

H'FCC0

8024

H'1CC0

8024

32 Bck

DMA transfer count register 6

TCR6 R/W

H'FCC0

8028

H'1CC0

8028

32 Bck

DMA channel control register 6

CHCR6

R/W*1 H'FCC0

802C H'1CC0

802C 32

Bck,

Pck*4

7

DMA source address register 7

SAR7 R/W

H'FCC0

8030

H'1CC0

8030

32 Bck

DMA destination address register 7

DAR7 R/W

H'FCC0

8034

H'1CC0

8034

32 Bck

DMA transfer count register 7

TCR7 R/W

H'FCC0

8038

H'1CC0

8038

32 Bck

DMA channel control register 7

CHCR7

R/W*1 H'FCC0

803C H'1CC0

803C 32

Bck,

Pck*4

8

DMA source address register 8

SAR8 R/W

H'FCC0

8040

H'1CC0

8040

32 Bck

DMA destination address register 8

DAR8 R/W

H'FCC0

8044

H'1CC0

8044

32 Bck

DMA transfer count register 8

TCR8 R/W

H'FCC0

8048

H'1CC0

8048

32 Bck

DMA channel control register 8

CHCR8

R/W*1 H'FCC0

804C H'1CC0

804C 32

Bck,

Pck*4

9

DMA source address register 9

SAR9 R/W

H'FCC0

8050

H'1CC0

8050

32 Bck

DMA destination address register 9

DAR9 R/W

H'FCC0

8054

H'1CC0

8054

32 Bck

DMA transfer count register 9

TCR9 R/W

H'FCC0

8058

H'1CC0

8058

32 Bck

DMA channel control register 9

CHCR9

R/W*1 H'FCC0

805C H'1CC0

805C 32

Bck,

Pck*4