14 cl status register (clsr) – Renesas SH7781 User Manual

Page 1023

20. Graphics Data Translation Accelerator (GDTA)

Rev.1.00 Jan. 10, 2008 Page 993 of 1658

REJ09B0261-0100

20.3.14

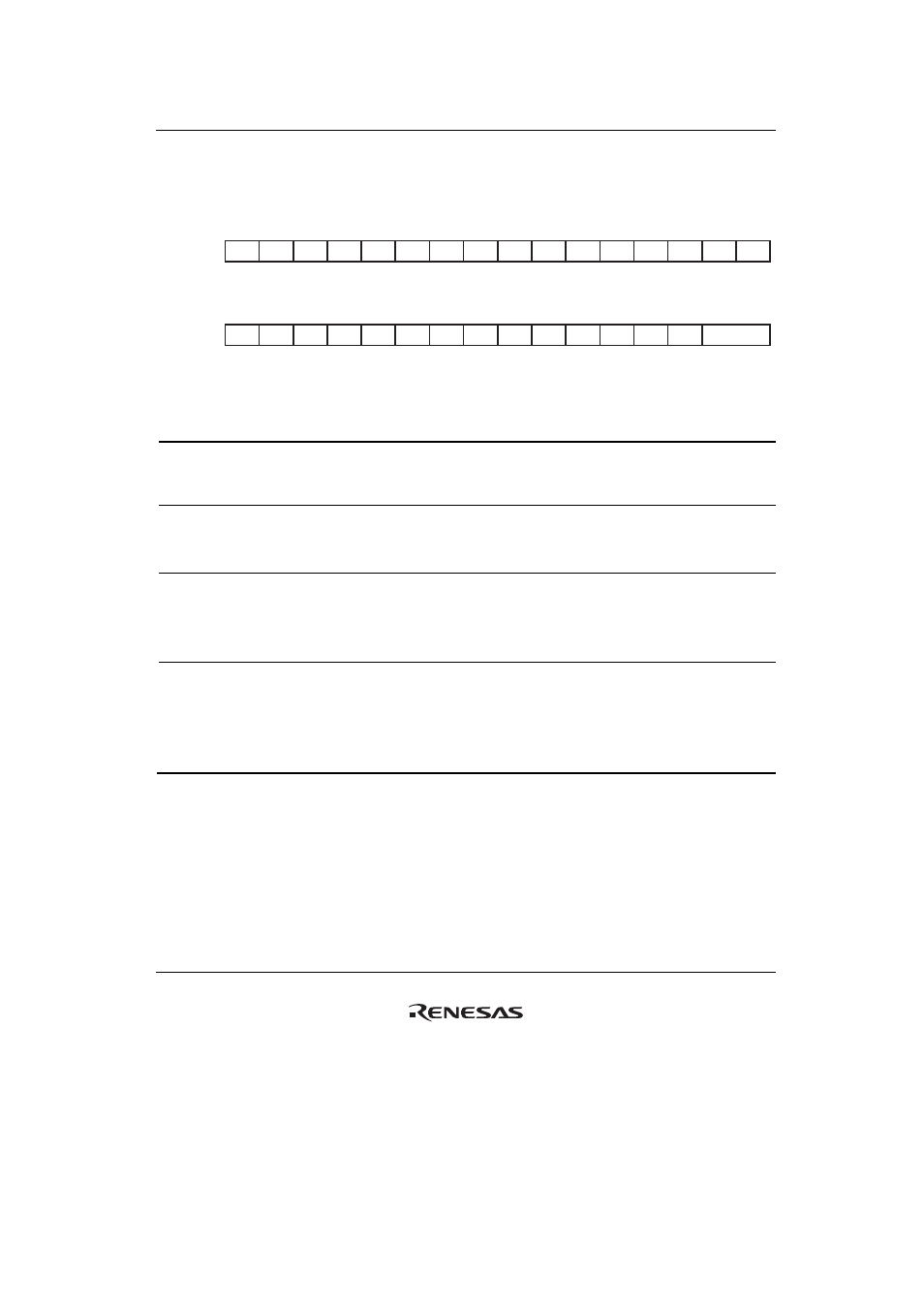

CL Status Register (CLSR)

CLSR is in the CL register block and indicates the internal states of the CL.

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

BIt:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

CL_CFS

CL_CFF

CLSR_

EXE

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

R

R

R

R

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

BIt:

Initial value:

R/W:

Bit Bit

Name

Initial

Value R/W Description

31 to 4

⎯ All

0

⎯ Reserved

These bits are always read as 0. The write value should

always be 0.

3

CLSR_EXE

0

R

CL execution state display

0: Stopped

1: Executing

2

CL_CFF

0

R

CL_CF (command FIFO) status display

Indicates the state of command buffer reception.

0: Command receivable

1: Command buffer full

1, 0

CL_CFS

0

R

Command pointer status display

00: CL_CF command parameter 1 setting wait state

01: CL_CF command parameter 2 setting wait state

10: CL_CF command parameter 3 setting wait state

11: CL_CF command parameter 4 setting wait state