1 mode register (simdr) – Renesas SH7781 User Manual

Page 1134

22. Serial I/O with FIFO (SIOF)

Rev.1.00 Jan. 10, 2008 Page 1104 of 1658

REJ09B0261-0100

22.3.1

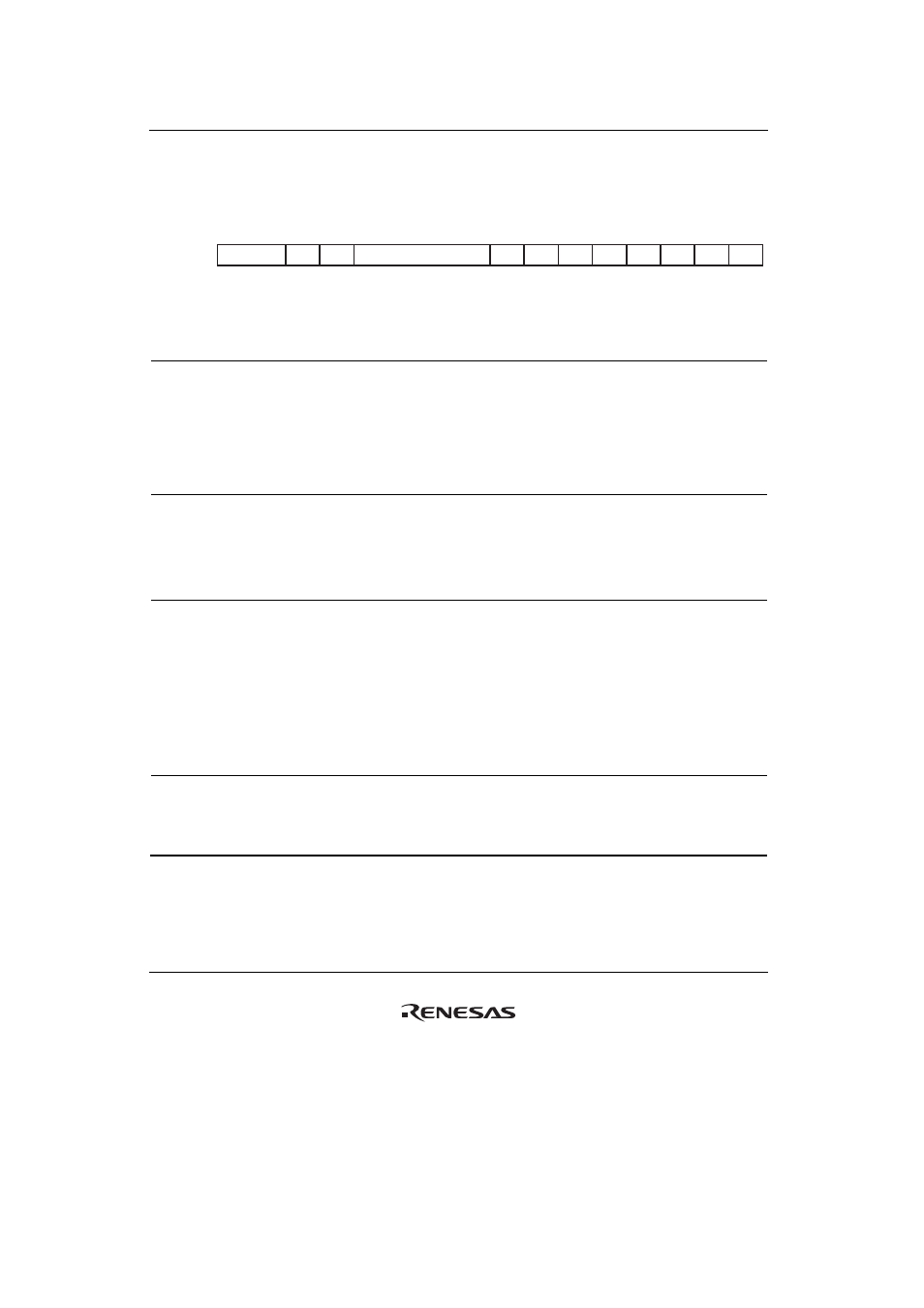

Mode Register (SIMDR)

SIMDR is a 16-bit readable/writable register that sets the SIOF operating mode.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

—

—

—

—

SYN

CDL

SYN

CAC

RCIM

TXDIZ

FL[3:0]

REDG

SYN

CAT

TRMD[1:0]

R

R

R

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

BIt:

Initial value:

R/W:

Bit Bit

Name

Initial

Value R/W Description

15, 14

TRMD[1:0]

10

R/W

Transfer Mode 1, 0

These bits select transfer mode shown in table 22.4.

00: Slave mode 1

01: Slave mode 2

10: Master mode 1

11: Master mode 2

13

SYNCAT

0

R/W

SIOF_SYNC Pin Valid Timing

Indicates the position of the SIOF_SYNC signal to be

output as a synchronous pulse.

0: At the start bit data of frame

1: At the last bit data of slot

12

REDG

0

R/W

Receive Data Sampling Edge

0: The SIOF_RXD signal is sampled at the falling edge

of SIOF_SCK

1: The SIOF_RXD signal is sampled at the rising edge

of SIOF_SCK

Note: The timing to transmit the SIOF_TXD signal is at

the opposite edge of the timing that samples the

SIOF_RXD. This bit is valid only in master

mode.

11 to 8

FL[3:0]

0000

R/W

Frame Length 3 to 0

These bits specify the flame length of transfer data

format. For the correspondence among setting values,

data length, and frame length, see table 22.7.