6 pcic module signal timing – Renesas SH7781 User Manual

Page 1629

32. Electrical Characteristics

Rev.1.00 Jan. 10, 2008 Page 1599 of 1658

REJ09B0261-0100

32.3.6

PCIC Module Signal Timing

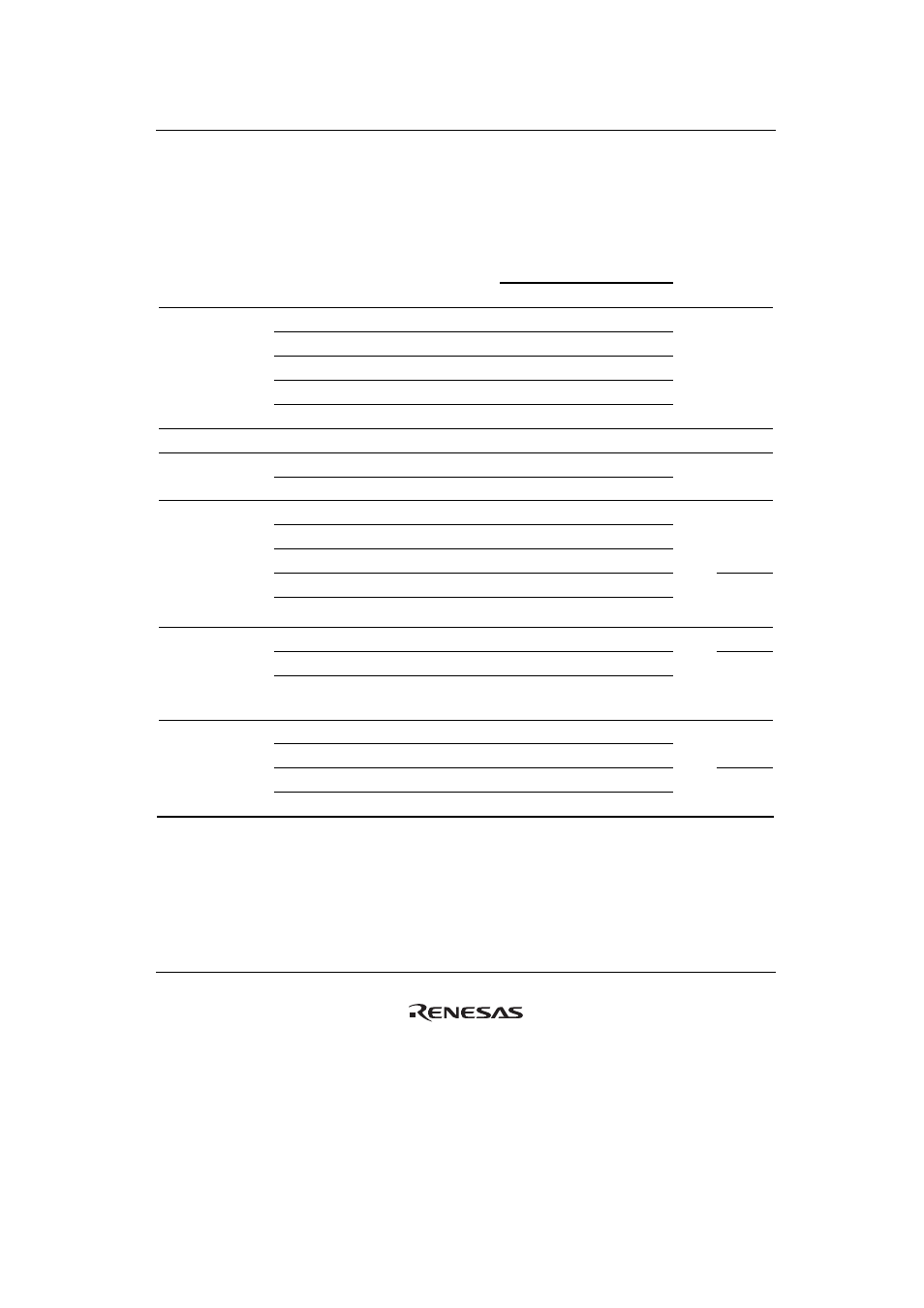

Table 32.11 PCIC Signal Timing (in PCIREQ/PCIGNT Non-Port Mode) (1)

Conditions: V

DDQ

= 3.0 to 3.6 V, V

DD

= 1.1 V, T

a

= –40 to 85

°C, C

L

= 30 pF

33 MHz

66 MHz

Pin

Item

Symbol Min. Max. Min. Max. Unit Figure

Clock period

t

PCICYC

30 — 15 30 ns 32.37

Clock pulse width (high) t

PCIHIGH

11 — 6 —

Clock pulse width (low)

t

PCIr

11

—

6

—

Clock rise time

t

PCIf

— 4 — 1.5

PCICLK

Clock fall time

t

NCDAD1

— 4 — 1.5

PCIRESET

Output data delay time

t

PCIVAL

— 10 — 10 ns 32.38

Input setup time

t

PCISU

3 — 3 — ns

32.39

IDSEL

Input hold time

t

PCIH

1.5 — 1.5 —

Output data delay time

t

PCIVAL

2 10

2 6 ns

32.38

Tri-state drive delay time t

PCION

2 10

2 6

Tri-state Hi-Z delay time t

PCIOFF

2 12

2 6

Input setup time

t

PCISU

3 — 3 — 32.39

AD31 to AD0,

C/

BE3 to C/BE0,

PCIFRAME,

PAR,

IRDY,

TRDY, STOP,

LOCK, PERR,

DEVSEL,

Input hold time

t

PCIH

1.5 — 1.5 —

Output data delay time

t

PCIVAL

2 10

2 6 ns

32.38

Input setup time

t

PCISU

3 — 3 — 32.39

REQ0/REQOUT,

GNT0/GNTIN

REQ1, REQ2,

REQ3, GNT1,

GNT2, GNT3

Input hold time

t

PCIH

1.5 — 1.5 —

Tri-state drive delay time t

PCION

— 10 — 10 ns 32.38

Tri-state Hi-Z delay time t

PCIOFF

— 12 — 12

SERR, INTA,

INTB, INTC,

INTD

Input setup time

t

PCISU

3 — 3 — 32.39

Input hold time

t

PCIH

1.5 — 1.5 —