Renesas SH7781 User Manual

Page 483

11. Local Bus State Controller (LBSC)

Rev.1.00 Jan. 10, 2008 Page 453 of 1658

REJ09B0261-0100

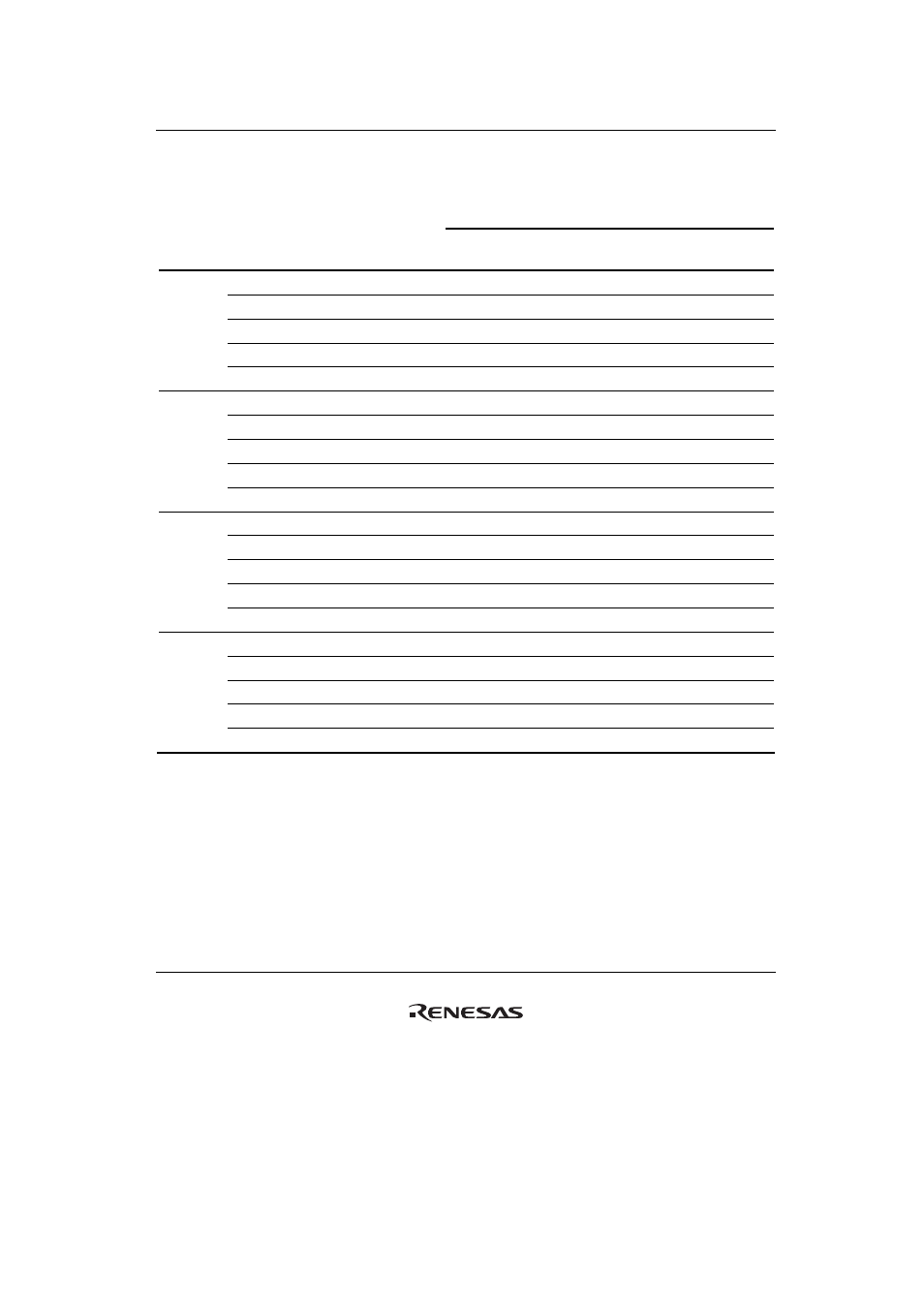

Table 11.19 Register Settings for Divided-Up

DACKn Output in DMA1 Transfer Using the

SRAM/Burst ROM/Byte Control SRAM Interfaces

Not Divided

Divided

Bus Width

[Bit]

Access Size in

DMA Transfer

Bus Cycle

Number

IWRRD, IWRRS, or

IWW in CSnBCR

ADS and ADH in

CSnWCR.

ADS and ADH

inCSnWCR

Byte 1

⎯

⎯ Undividable

Word 2

⎯

B'000

B'111 to B'001

Longword 4

⎯

B'000

B'111 to B'001

16 bytes

16

B'000

B'000

B'111 to B'001

8

32 bytes

32

⎯

B'000

B'111 to B'001

Byte 1

⎯

⎯ Undividable

Word 1

⎯

⎯ Undividable

Longword 2

⎯

B'000

B'111 to B'001

16 bytes

8

B'000

B'000

B'111 to B'001

16

32 bytes

16

⎯

B'000

B'111 to B'001

Byte 1

⎯

⎯ Undividable

Word 1

⎯

⎯ Undividable

Longword 1

⎯

⎯ Undividable

16 bytes

4

B'000

B'000

B'111 to B'001

32

32 bytes

8

⎯

B'000

B'111 to B'001

64 Byte

1

⎯

⎯ Undividable

Word 1

⎯

⎯ Undividable

Longword

1

⎯

⎯ Undividable

16 bytes

4

B'000

B'000

B'111 to B'001

32

bytes

4

⎯

B'000

B'111 to B'001

Note: "

⎯" means an arbitrary setting value. When transfer is done in a single bus cycle,

DACKn

is not divided up because

DACKn is output once in DMA1 transfer.