15 pins multiplexed with other modules functions, 16 register settings for divided-up dackn output – Renesas SH7781 User Manual

Page 482

11. Local Bus State Controller (LBSC)

Rev.1.00 Jan. 10, 2008 Page 452 of 1658

REJ09B0261-0100

11.5.14

Mode Pin Settings and General Input Output Port Settings about Data Bus Width

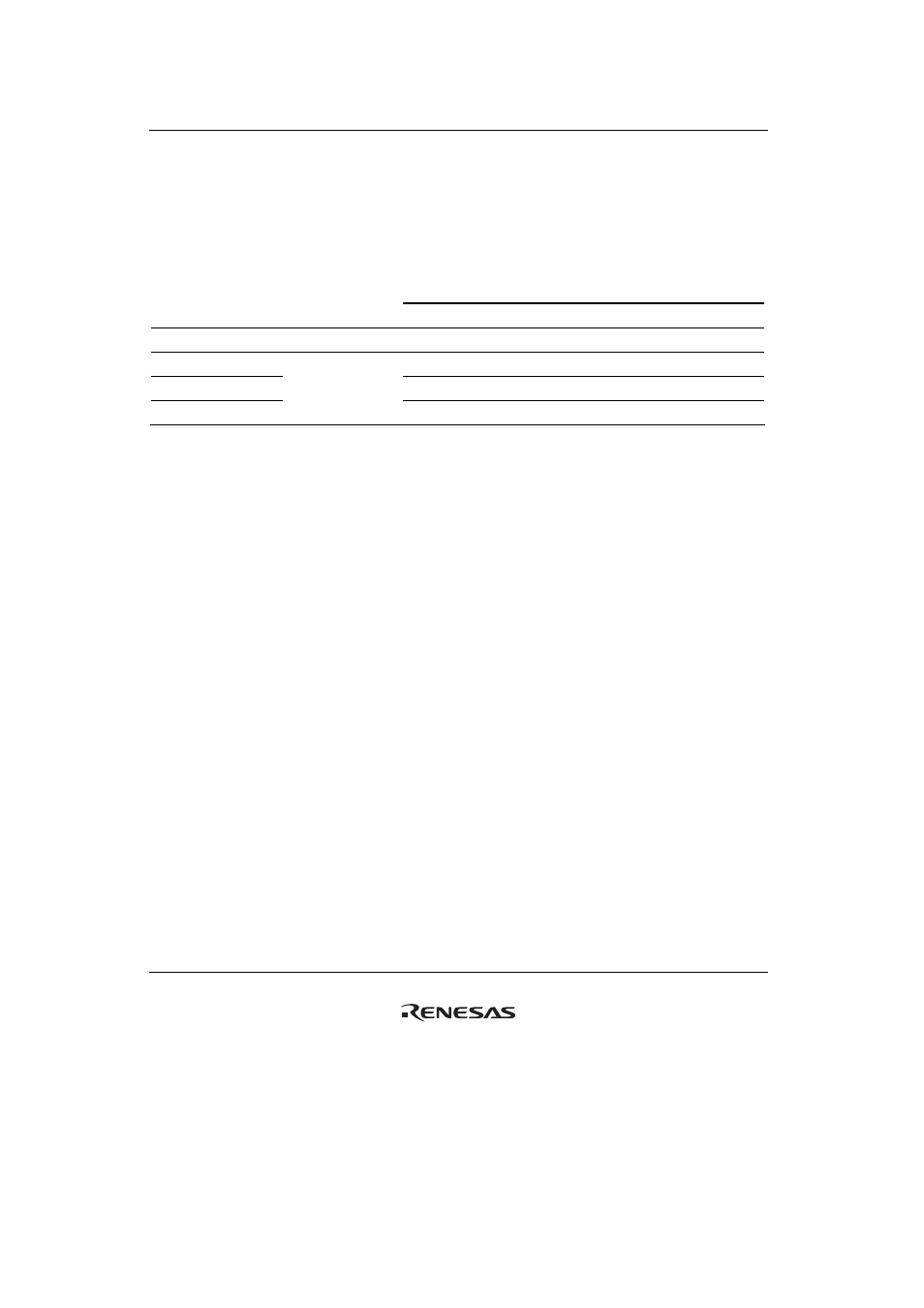

Table 11.18 shows the examples of MODE pin settings and port settings (GPIO port control

register) related to the selection of the data bus width used in the local bus.

Table 11.18 MODE Pin Settings and Port Settings Related to Data Bus Width Selection

GPIO Port Control Register

Data Bus

Width

Data Pins MODE12 MODE11 PACR

PBCR

PCCR

PDCR

PFCR

PGCR

64 bits

D63 to D0

H

L

H'0000 H'0000 H'0000 H'0000 H'0000 H'0000

32 bits

D31 to D0

Any

Any

Any

Any

Any

Any

H'0000

H'0000

16 bits

D16 to D0

Any

Any

Any

Any

Any

Any

8 bits

D7 to D0

Any

Any

Any

Any

Any

Any

Legend:

L: Low

level

H: High level

Note: Concerning "any", setting should be correspondent to the system.

11.5.15

Pins Multiplexed with Other Modules Functions

Some pins used by the LBSC are multiplexed with general input output port (GPIO) and functions

used in other peripheral modules. The pins to be used by the LBSC should start access after setting

these pins to the LBSC functions with GPIO register. For example, when PCMCIA interface is

used, the functions of CE2A and CE2B should be enabled with the GPIO bit in PIMSELR and the

GPIO bit in PLCR before starting access.

11.5.16

Register Settings for Divided-Up

DACKn Output

When the access size of DMAC1 transfer related to the local bus space is larger than the data bus

width, multiple bus cycles are generated. When multiple bus cycles are generated and

CS is

negated between bus cycles,

DACKn output is divided up, in the same way as CS.

Tables 11.19 to 11.22 shows the register settings when

DACKn output is not divided up in DMA1

transfer and when it is divided up.