2 user mode interrupt disable function – Renesas SH7781 User Manual

Page 328

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 298 of 1658

REJ09B0261-0100

10.3.2

User Mode Interrupt Disable Function

(1)

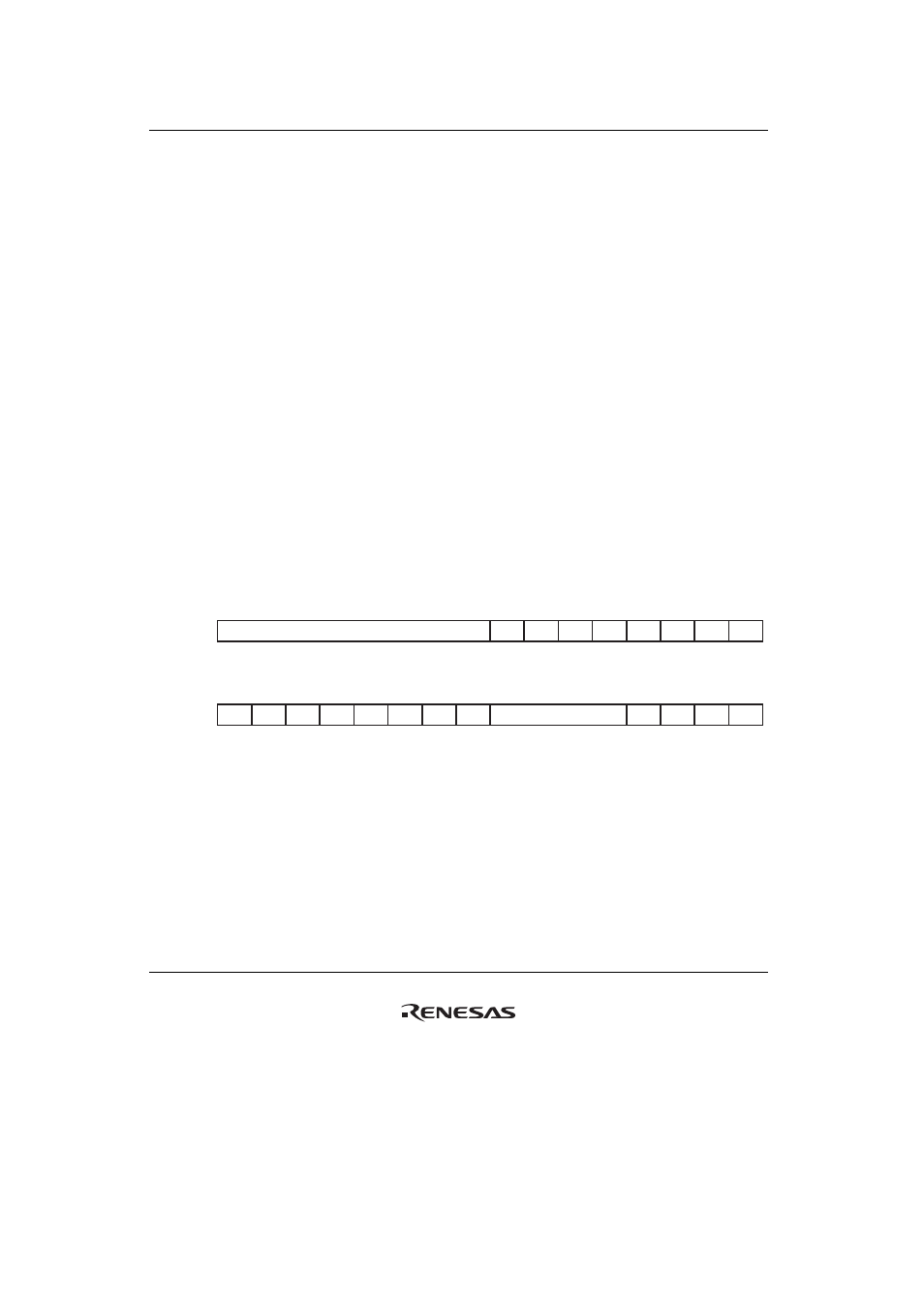

User Interrupt Mask Level Setting Register (USERIMASK)

USERIMASK is a 32-bit readable and conditionally writable register that sets the acceptable

interrupt level. This register is allocated to the 64-Kbyte page that the other registers in the INTC

are not allocated. Therefore, only this register can be set to be accessible in user mode by changing

the address to area 7 address through the MMU.

The interrupts that the level is lower than the level set in the UIMASK bits are masked. When H'F

is set in the UIMASK bit, all interrupts other than the NMI are masked.

The interrupts that the level is higher than the level set in the UIMASK bits are accepted under the

following conditions. The corresponding interrupt mask bit in the interrupt mask register is cleared

to 0 (the interrupt is enabled). The IMASK bit in SR is set lower than its interrupt level.

The value of the UIMASK bit does not change even if an interrupt is accepted.

USERIMASK is initialized to H'0000 0000 (all interrupts are enabled) by a power-on reset or

manual reset.

To prevent incorrect writing, this register should not be written to unless bits 31 to 24 are set to

H'A5.

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

R

R

R

R

R

R

R

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

⎯

⎯

⎯

⎯

UIMASK

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

R

R

R

R

R/W

R/W

R/W

R/W

R

R

R

R

R

R

R

R

Bit:

Initial value:

R/W:

Code for writing (H'A5)