Renesas SH7781 User Manual

Page 1213

24. Multimedia Card Interface (MMCIF)

Rev.1.00 Jan. 10, 2008 Page 1183 of 1658

REJ09B0261-0100

Bit Bit

Name

Initial

Value R/W

Description

0 REQ 0 R

Interrupt

Request

Indicates whether an interrupt is requested or not.

When any of the INTSTR0, INTSTR1 and INTSTR2

flags is set, this bit is set to 1. Setting of the INTSTR0,

INTSTR1 and INTSTR2 flags is controlled by the

enable bits in INTCR0, INTSTR1 and INTCR2.

0: No interrupt requested.

1: Interrupt requested.

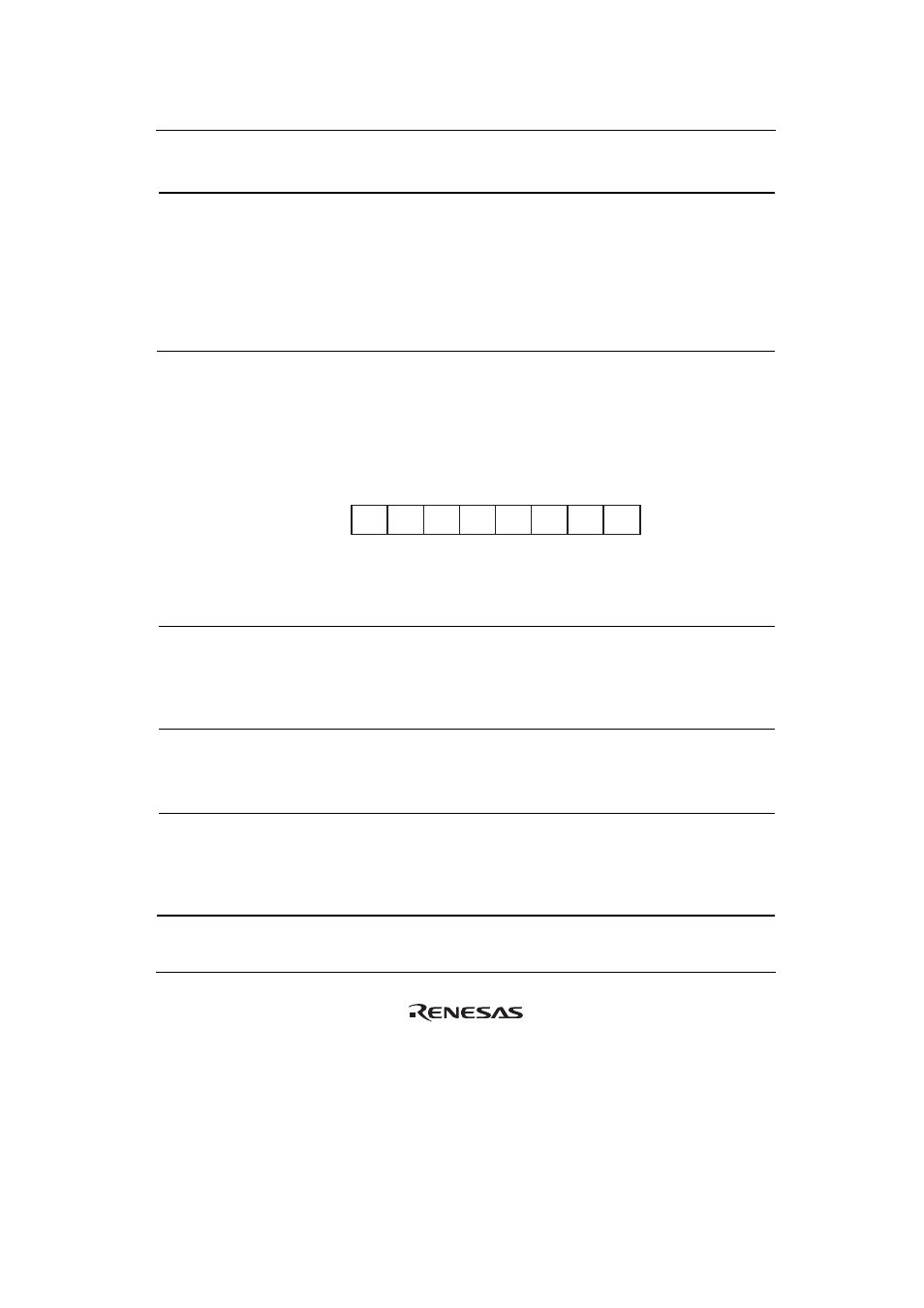

24.3.5

Interrupt Control Registers 0 to 2 (INTCR0 to INTCR2)

The INTCR registers enable or disable interrupts.

(1)

INTCR0

Bit:

Initial value:

R/W:

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

0

R/W

FEIE

FFIE DRPIE DTIE CRPIE CMDIE

DBS

YIE

R/W

R/W

R/W

R/W

R/W

R/W

R/W

BTIE

Bit Bit

Name

Initial

Value R/W Description

7

FEIE

0

R/W

FIFO Empty Interrupt Flag Setting Enable

0: Disables FIFO empty interrupt (disables FEI flag

setting).

1. Enables FIFO empty interrupt (enables FEI flag

setting).

6

FFIE

0

R/W

FIFO Full Interrupt Flag Setting Enable

0: Disables FIFO full interrupt (disables FFI flag

setting).

1: Enables FIFO full interrupt (enables FFI flag setting).

5

DRPIE

0

R/W

Data Response Interrupt Flag Setting Enable

0: Disables data response interrupt (disables DPRI flag

setting).

1: Enables data response interrupt (enables DPRI flag

setting).