8 channel match flag register (ccmfr) – Renesas SH7781 User Manual

Page 1501

29. User Break Controller (UBC)

Rev.1.00 Jan. 10, 2008 Page 1471 of 1658

REJ09B0261-0100

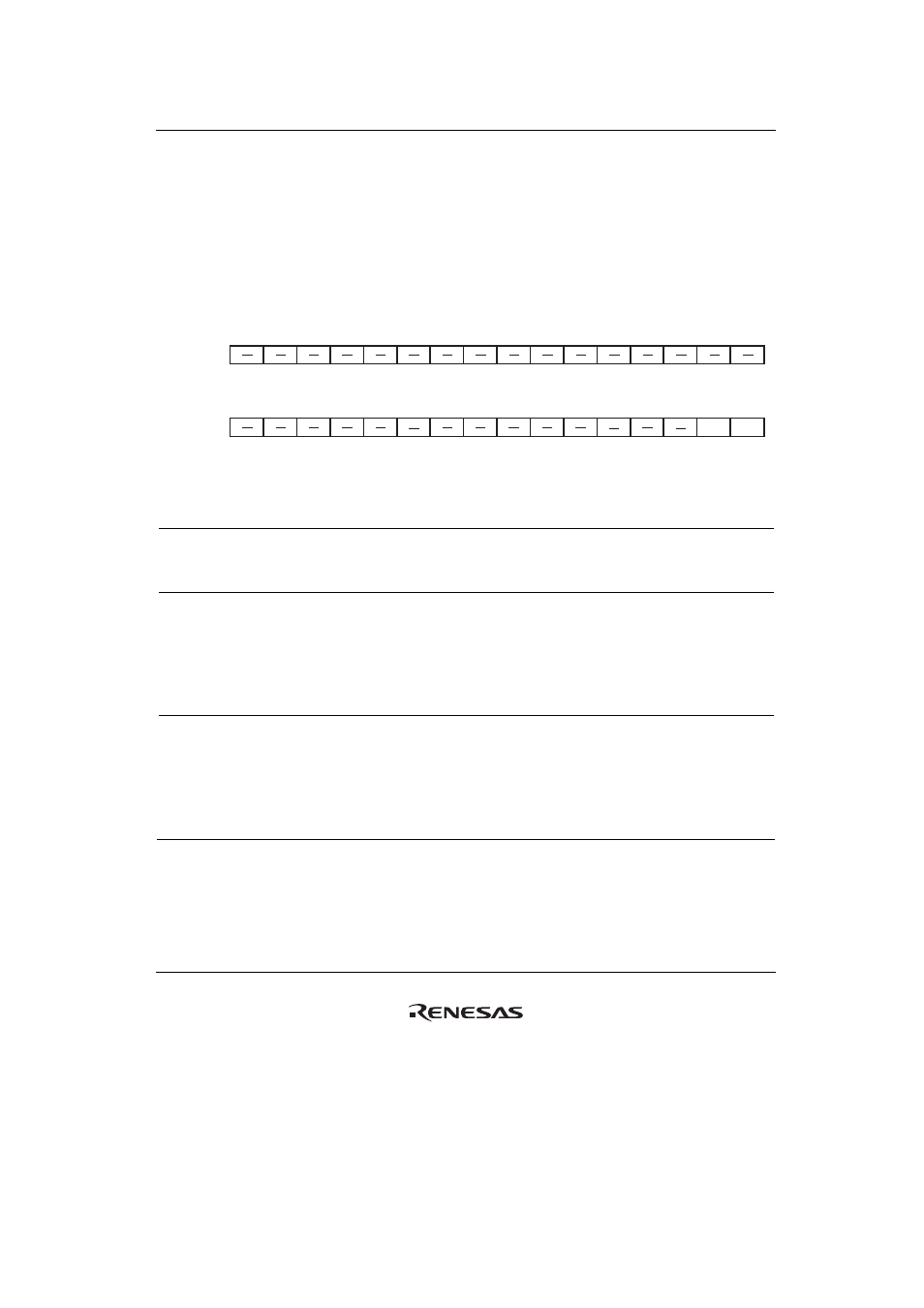

29.2.8

Channel Match Flag Register (CCMFR)

CCMFR is a readable/writable 32-bit register which indicates whether or not the match conditions

have been satisfied for each channel. When a channel match condition has been satisfied, the

corresponding flag bit is set to 1. To clear the flags, write the data containing value 0 for the bits to

be cleared and value 1 for the other bits to this register. (The logical AND between the value

which has been written and the current register value is actually written to the register.) Sequential

operation using multiple channels is available by using these match flags.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

MF1

MF0

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R/W

R/W

Bit :

Initial value :

R/W:

Bit :

Initial value :

R/W:

Bit Bit

Name

Initial

Value R/W

Description

31 to 2

—

All 0

R

Reserved

For read/write in this bit, refer to General Precautions

on Handling of Product.

1

MF1

0

R/W

Channel 1 Condition Match Flag

This flag is set to 1 when the channel 1 match

condition has been satisfied. To clear the flag, write 0

to this bit.

0: Channel 1 match condition has not been satisfied.

1: Channel 1 match condition has been satisfied.

0

MF0

0

R/W

Channel 0 Condition Match Flag

This flag is set to 1 when the channel 0 match

condition has been satisfied. To clear the flag, write 0

to this bit.

0: Channel 0 match condition has not been satisfied.

1: Channel 0 match condition has been satisfied.