4 user break debugging support function – Renesas SH7781 User Manual

Page 1510

29. User Break Controller (UBC)

Rev.1.00 Jan. 10, 2008 Page 1480 of 1658

REJ09B0261-0100

29.4

User Break Debugging Support Function

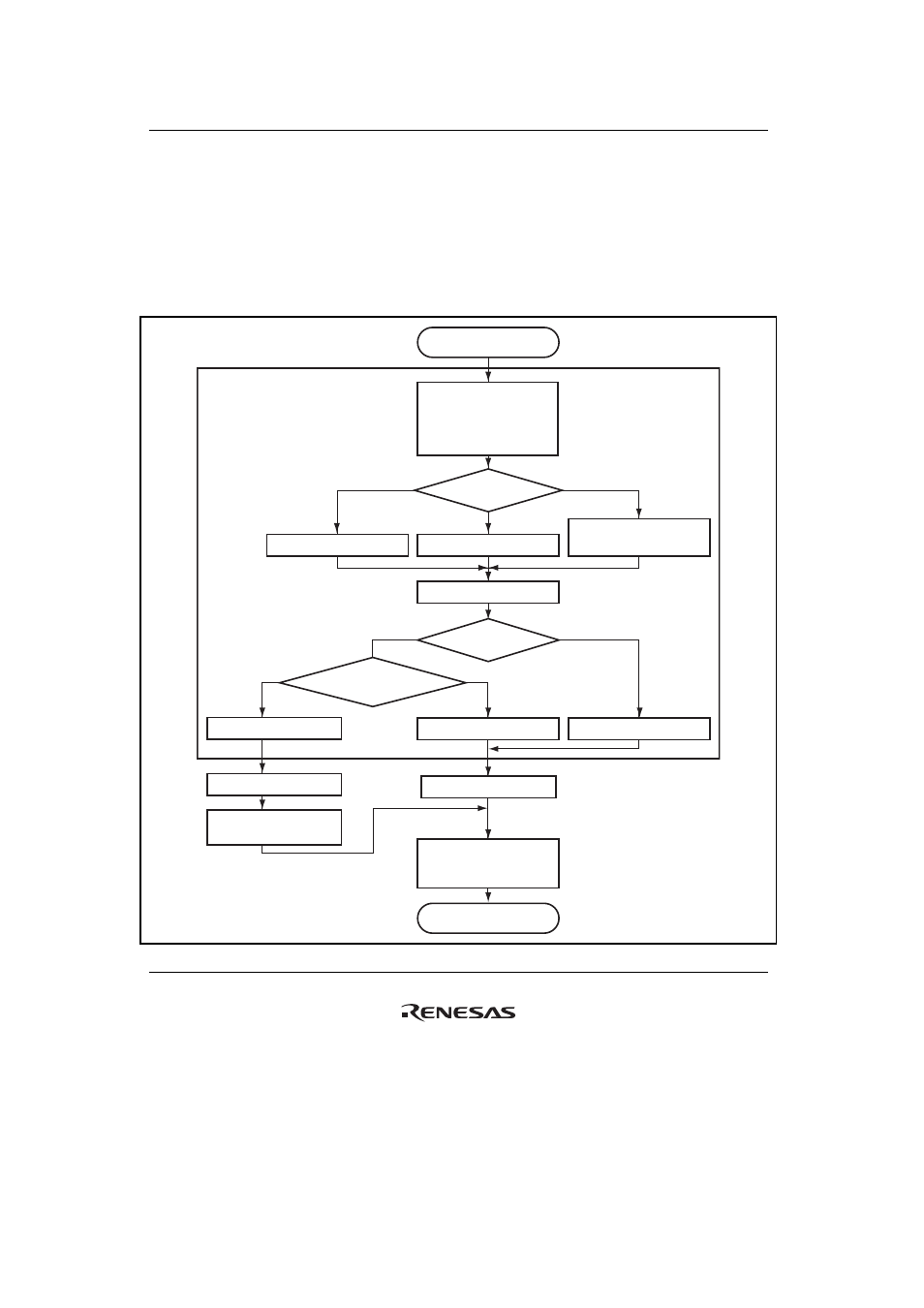

By using the user break debugging support function, the branch destination address can be

modified when the CPU accepts the user break request. Specifically, setting the UBDE bit of

break control register CBCR to 1 allows branching to the address indicated by DBR instead of

branching to the address indicated by the [VBR

+ offset]. Figure 29.2 shows the flowchart of the

user break debugging support function.

SPC

← PC

SSR

← SR

SR.BL

← B'1

SR.MD

← B'1

SR.RB

← B'1

Exception/interrupt

is generated

Exception

Exception/interrupt/trap?

Trap

Interrupt

PC

← H'A000 0000

PC

← VBR + vector offset

Execute RTE instruction

PC

← SPC

SR

← SSR

SGR

← R15

PC

← DBR

Debugging program

R15

← SGR

(STC instruction)

Reset exception?

(CBCR.UBDE == 1)

&& (user break)?

Exception operation ends

INTEVT

← Interrupt code

EXPEVT

← Exception code

Yes

No

No

Yes

Hardware operations

Exception handling routine

TRA

← TRAPA (imm)

EXPEVT

← H'160

Figure 29.2 Flowchart of User Break Debugging Support Function