Renesas SH7781 User Manual

Page 317

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 287 of 1658

REJ09B0261-0100

(7)

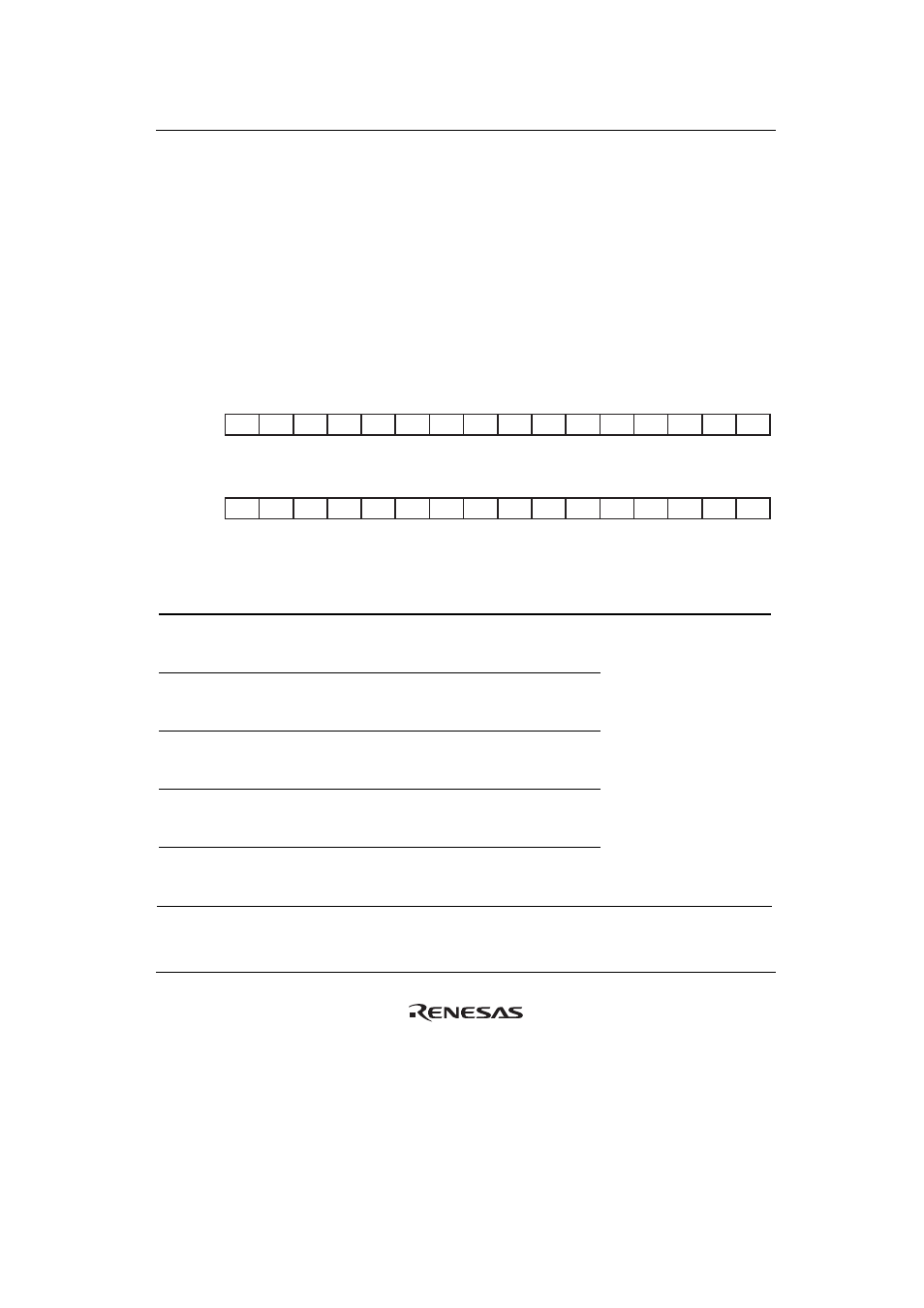

Interrupt Mask Register 2 (INTMSK2)

INTMSK2 is a 32-bit readable and conditionally writable register that sets masking for IRL

interrupt requests for input level pattern on the

IRL pins. To clear the mask setting for the

interrupt, write 1 to the corresponding bit in INTMSKCLR2. Writing 0 to the bits in INTMSK2

has no effect. By reading this register once after writing to this register or after clearing the mask

by setting IMTMSKCLR2, the time length necessary for reflecting the register value can be

assured (the value read is reflected to the mask status).

INTMSK2 settings are valid when the IRQ/

IRL3 to IRQ/IRL0 pins or IRQ/IRL7 to IRQ/IRL4

pins are used for encoded IRL interrupt inputs, and the corresponding IRL interrupt is not masked

by INTMSK1.

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

⎯

IM001

IM002

IM003

IM004

IM005

IM006

IM007

IM008

IM009

IM010

IM011

IM012

IM013

IM015 IM014

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

⎯

IM101

IM102

IM103

IM104

IM105

IM106

IM107

IM108

IM109

IM110

IM111

IM112

IM113

IM115 IM114

Bit:

Initial value:

R/W:

Bit Name

Initial

Value R/W Description

31

IM015

0

R/W

Masks the interrupt source

of

IRL3 to IRL0 = LLLL

(H'0).

30

IM014

0

R/W

Masks the interrupt source

of

IRL3 to IRL0 = LLLH

(H'1).

29

IM013

0

R/W

Masks the interrupt source

of

IRL3 to IRL0 = LLHL

(H'2).

[When read]

0: The interrupt is

accepted.

1: The interrupt is

masked.

[When written]

0: No effect

1: Masks the interrupt

28

IM012

0

R/W

Masks the interrupt source

of

IRL3 to IRL0 = LLHH

(H'3).

27

IM011

0

R/W

Masks the interrupt source

of

IRL3 to IRL0 = LHLL

(H'4).