6 processing states – Renesas SH7781 User Manual

Page 71

2. Programming Model

Rev.1.00 Jan. 10, 2008 Page 41 of 1658

REJ09B0261-0100

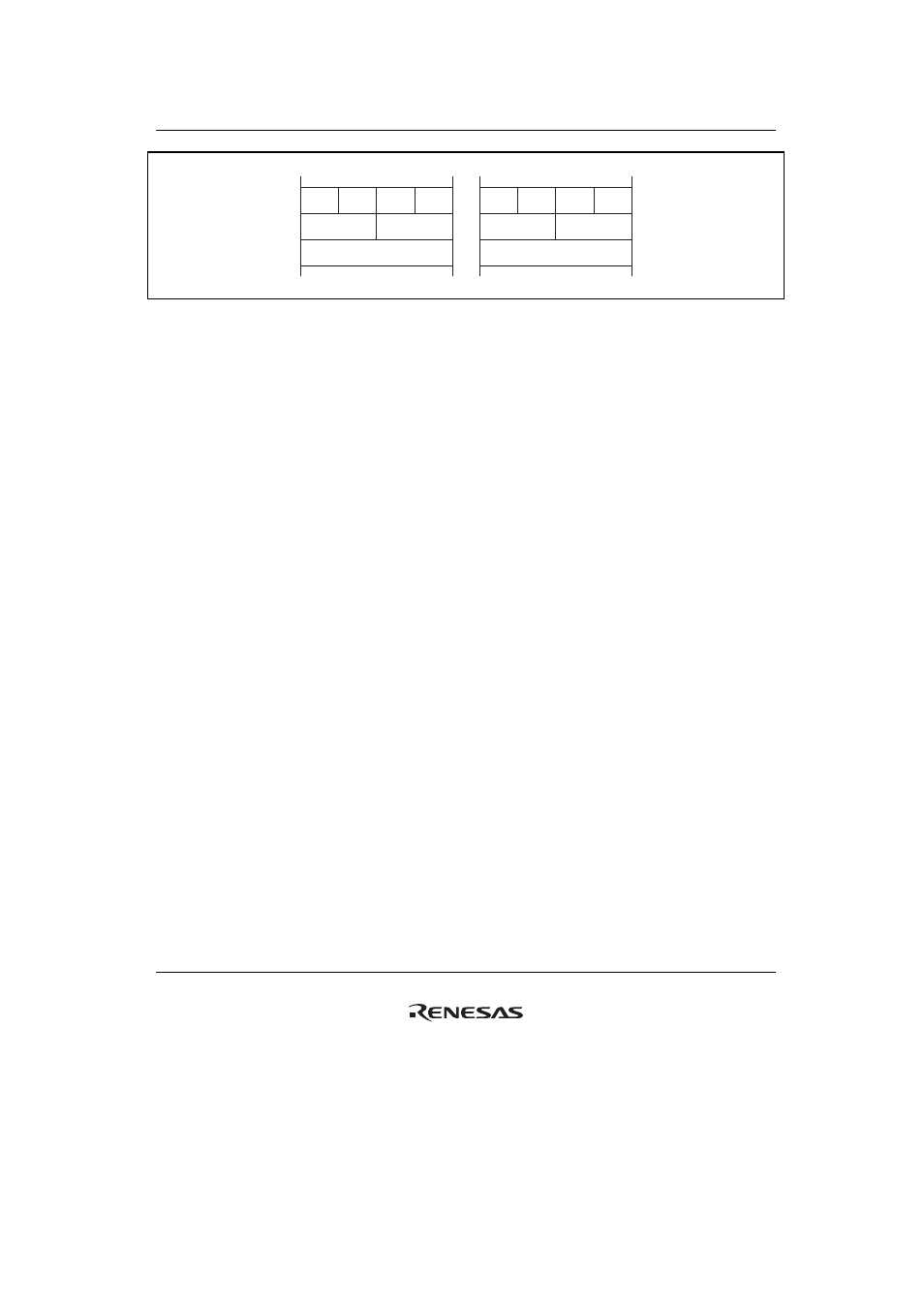

Address A

A

7

0 7

0 7

0 7

0

31

15

0 15

0

31

0

15

0

31

0

23

15

7

0

A + 1

A + 2

A + 3

Byte 0

Word 0

Longword

Word 1

Byte 1 Byte 2 Byte 3

A + 11

7

0 7

0 7

0 7

0

31

15

0

23

15

7

0

A + 10 A + 9

A + 8

Byte 3

Word 1

Longword

Word 0

Byte 2 Byte 1 Byte 0

Address A + 4

Address A + 8

Address A + 8

Address A + 4

Address A

Big endian

Little endian

Figure 2.7 Data Formats in Memory

For the 64-bit data format, see figure 2.5.

2.6

Processing States

This LSI has major three processing states: the reset state, instruction execution state, and power-

down state.

(1)

Reset State

In this state the CPU is reset. The reset state is divided into the power-on reset state and the

manual reset.

In the power-on reset state, the internal state of the CPU and the on-chip peripheral module

registers are initialized. In the manual reset state, the internal state of the CPU and some registers

of on-chip peripheral modules are initialized. For details, see register descriptions for each section.

(2)

Instruction Execution State

In this state, the CPU executes program instructions in sequence. The Instruction execution state

has the normal program execution state and the exception handling state.

(3)

Power-Down State

In a power-down state, CPU halts operation and power consumption is reduced. The power-down

state is entered by executing a SLEEP instruction. There are two modes in the power-down state:

sleep mode and standby mode. For details, see section 17, Power-Down mode.