Renesas SH7781 User Manual

Page 1336

26. Serial Sound Interface (SSI) Module

Rev.1.00 Jan. 10, 2008 Page 1306 of 1658

REJ09B0261-0100

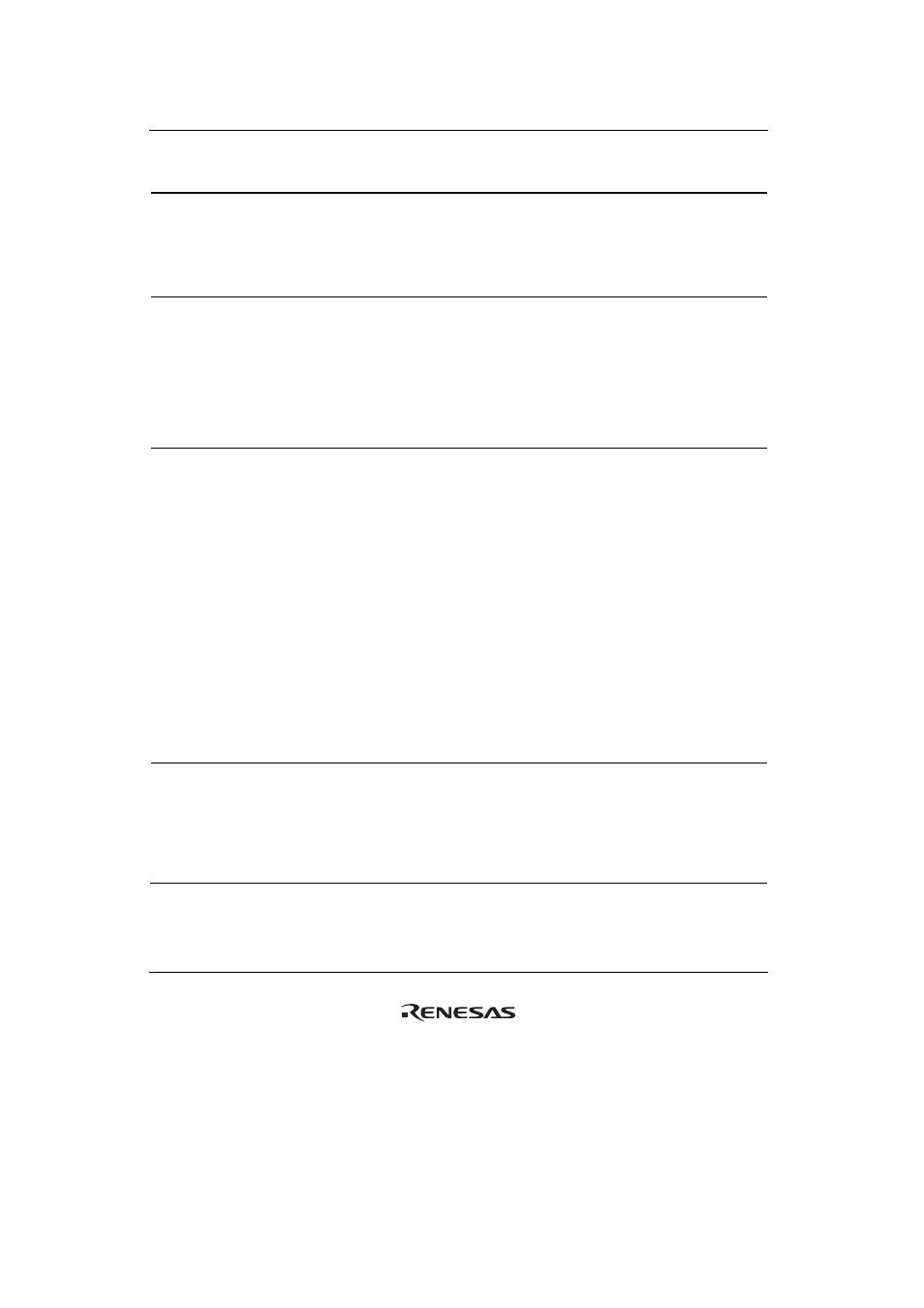

Bit Bit

Name

Initial

Value R/W Description

8

DEL

0

R/W

Serial Data Delay

Set this bit to 1, if CPEN=1

0: 1 clock cycle delay between SSI_WS and

SSI_SDATA

1: No delay between SSI_WS and SSI_SDATA

7

BREN

0

R/W

Burst Mode Enable

0: Burst mode is disabled.

1: Burst mode is enabled.

Burst mode is used only in compressed mode (CPEN =

1) and transmit mode. When burst mode is enabled the

SSI_SCK signal is gated. Clock pulses are output only

when there is valid serial data being output on

SSI_SDATA.

6 to 4

CKDV2

CKDV2

CKDV0

0

0

0

R/W

R/W

R/W

Serial Oversampling Clock Division Ratio

These bits define the division ratio between

oversampling clock (SSI_CLK) and the serial bit clock

(SSI_SCK).

These bits are ignored if SCKD = 0.

The serial bit clock is used for the shift register and is

provided on the SSI_SCK pin.

000: (Serial bit clock frequency = oversampling clock frequency/1)

001: (Serial bit clock frequency = oversampling clock frequency/2)

010: (Serial bit clock frequency = oversampling clock frequency/4)

011: (Serial bit clock frequency = oversampling clock frequency/8)

100: (Serial bit clock frequency = oversampling clock frequency/16)

101: (Serial bit clock frequency = oversampling clock frequency/6)

110: (Serial bit clock frequency = oversampling clock frequency/12)

111: Setting prohibited

3 MUEN

0

R/W

Mute

Enable

0: The SSI module is not muted

1: The SSI module is muted

When the SSI module is muted in transmit mode, the

SSIn_SDATA pin is always low regardless of the

padding polarity selected.