3 system control register (spscr) – Renesas SH7781 User Manual

Page 1191

23. Serial Peripheral Interface (HSPI)

Rev.1.00 Jan. 10, 2008 Page 1161 of 1658

REJ09B0261-0100

23.3.3

System Control Register (SPSCR)

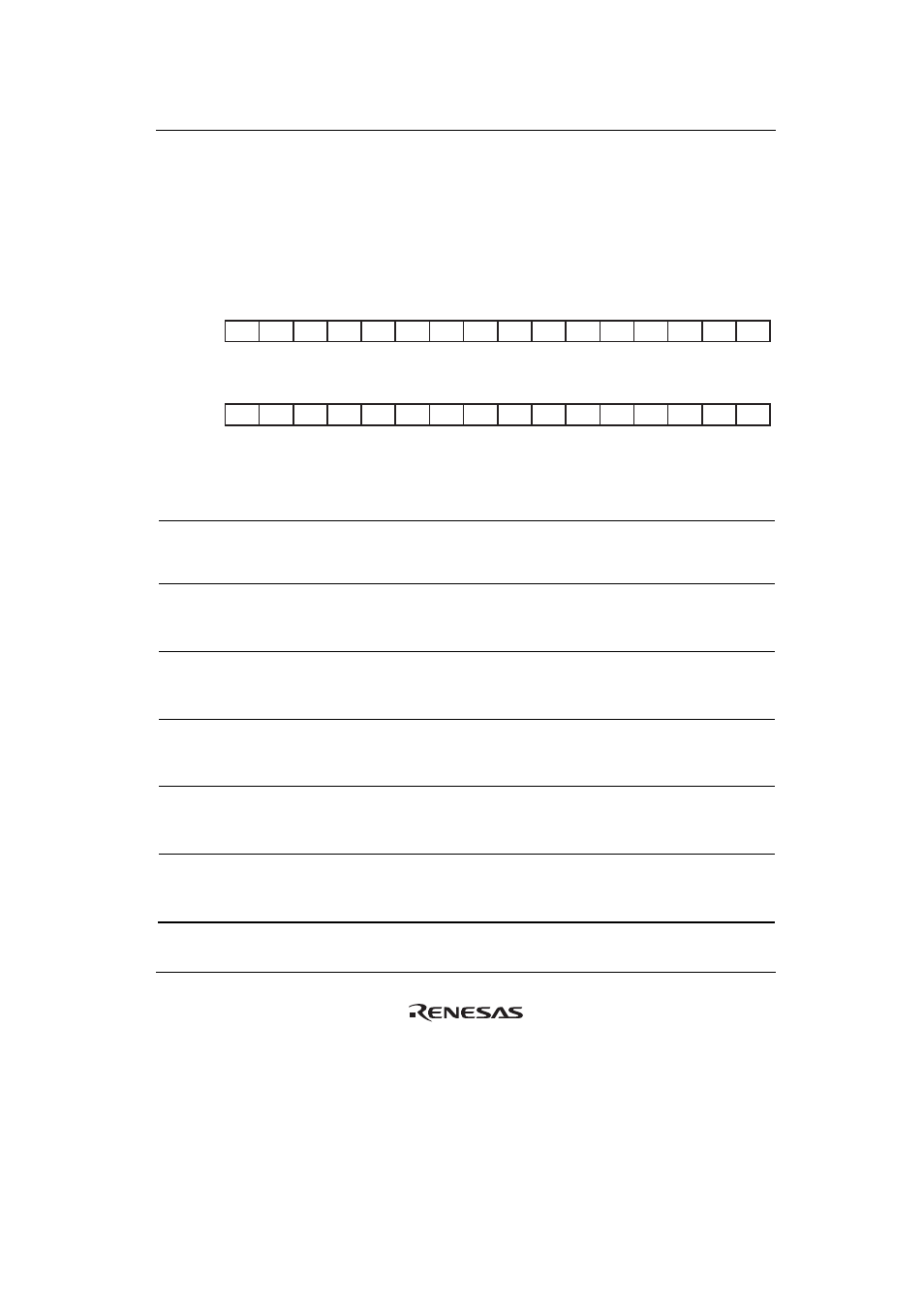

SPSCR is a 32-bit readable/writable register that enables or disables interrupts or FIFO mode,

selects either LSB first or MSB first in transmitting/receiving data, and master or slave mode.

If any of the FFEN, LMSB, CSA, or MASL bit values are changed, the module will undergo a

software reset.

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Bit:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

1

0

0

0

0

0

0

0

MASL

TXDE

RXDE

ROIE

TFIE

CSA

CSV

LMSB

FFEN

RFIE

RHIE

RNIE

THIE

TEIE

—

—

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

R

Bit:

Initial value:

R/W:

Bit Bit

Name

Initial

Value R/W

Description

31 to 14

⎯ All

0

R

Reserved

These bits are always read as an undefined value. The

write value should always be 0.

13

TEIE

0

R/W

Transmit FIFO Empty Interrupt Enable

0: Transmit FIFO empty interrupt disabled

1: Transmit FIFO empty interrupt enabled

12

THIE

0

R/W

Transmit FIFO Halfway Interrupt Enable

0: Transmit FIFO halfway interrupt disabled

1: Transmit FIFO halfway interrupt enabled

11 RNIE 0

R/W

Receive

FIFO

Not Empty Interrupt Enable

0: Receive FIFO not empty interrupt disabled

1: Receive FIFO not empty interrupt enabled

10

RHIE

0

R/W

Receive FIFO Halfway Interrupt Enable

0: Receive FIFO halfway interrupt disabled

1: Receive FIFO halfway interrupt enabled

9

RFIE

0

R/W

Receive FIFO Full Interrupt Enable

0: Receive FIFO full interrupt disabled

1: Receive FIFO full interrupt enabled