3 command code register (flcmcdr) – Renesas SH7781 User Manual

Page 1378

27. NAND Flash Memory Controller (FLCTL)

Rev.1.00 Jan. 10, 2008 Page 1348 of 1658

REJ09B0261-0100

Bit Bit

Name

Initial

Value R/W Description

16

DOCMD1 0

R/W

First Command Stage* Execution Specification

Specifies whether the first command stage* is executed

in command access mode.

0: Does not execute the first command stage

1: Executes the first command stage

15 to 0

SCTCNT

[15:0]

H'0000 R/W Sector

Transfer Count Specification

Specify the number of sectors to be read continuously

in sector access mode. These bits are counted down for

each sector transfer end, and stop when they reach 0.

When accessing one sector, set SCTCNT to 1.

Note: * For command stage, address stage, and data stage, see figure 27.2.

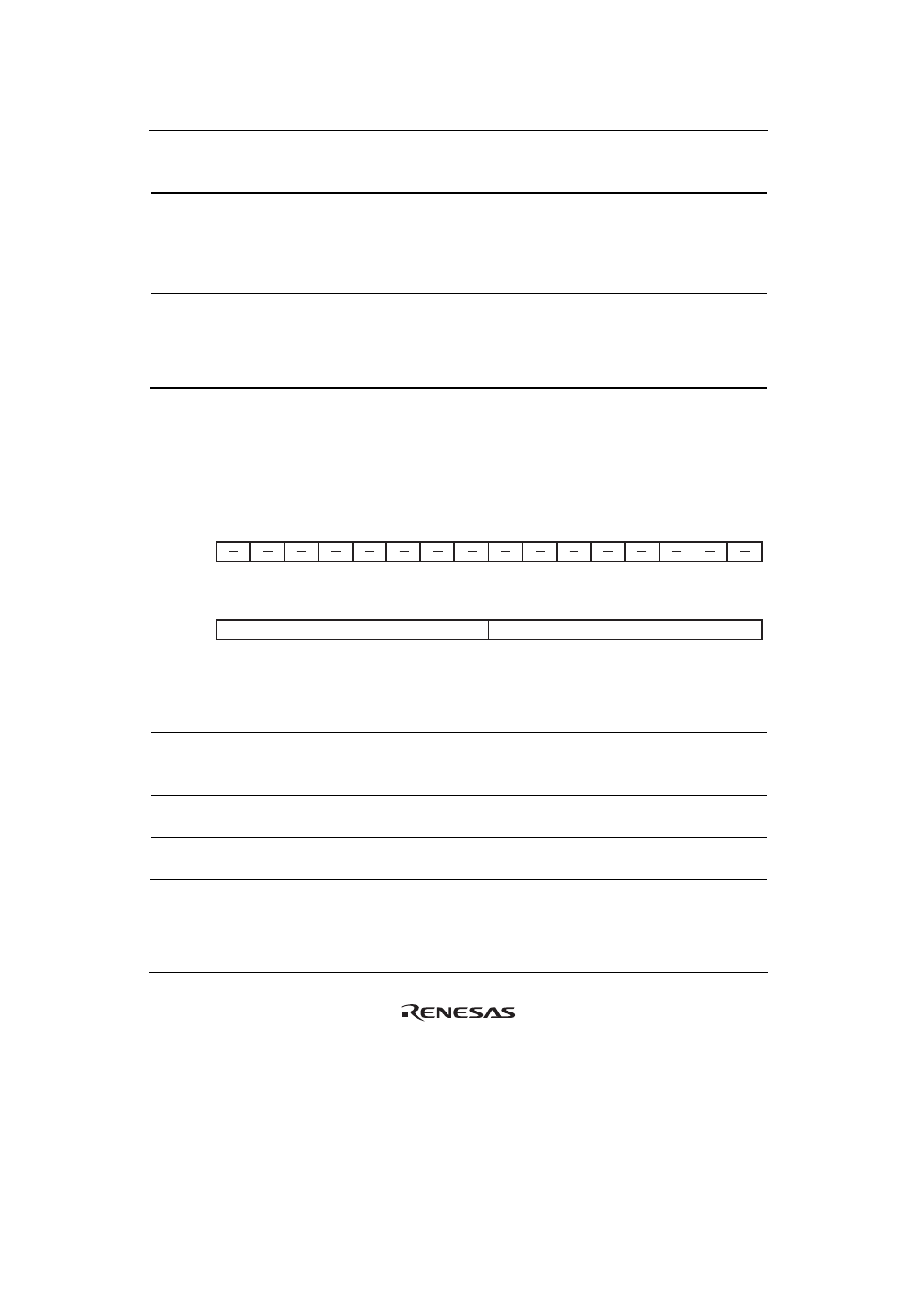

27.3.3

Command Code Register (FLCMCDR)

FLCMCDR is a 32-bit readable/writable register that specifies a command to be issued in

command access or sector access.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit:

Initial value:

R/W:

Bit:

Initial value:

R/W:

CMD[15:8]

CMD[7:0]

Bit Bit

Name

Initial

Value R/W Description

31 to 16 —

All 0

R

Reserved

These bits are always read as 0. The write value should

always be 0.

15 to 8

CMD[15:8] H'00

R/W

Specify a command code to be issued in the second

command stage.

7 to 0

CMD[7:0]

H'00

R/W

Specify a command code to be issued in the first

command stage.