Renesas SH7781 User Manual

Page 679

13. PCI Controller (PCIC)

Rev.1.00 Jan. 10, 2008 Page 649 of 1658

REJ09B0261-0100

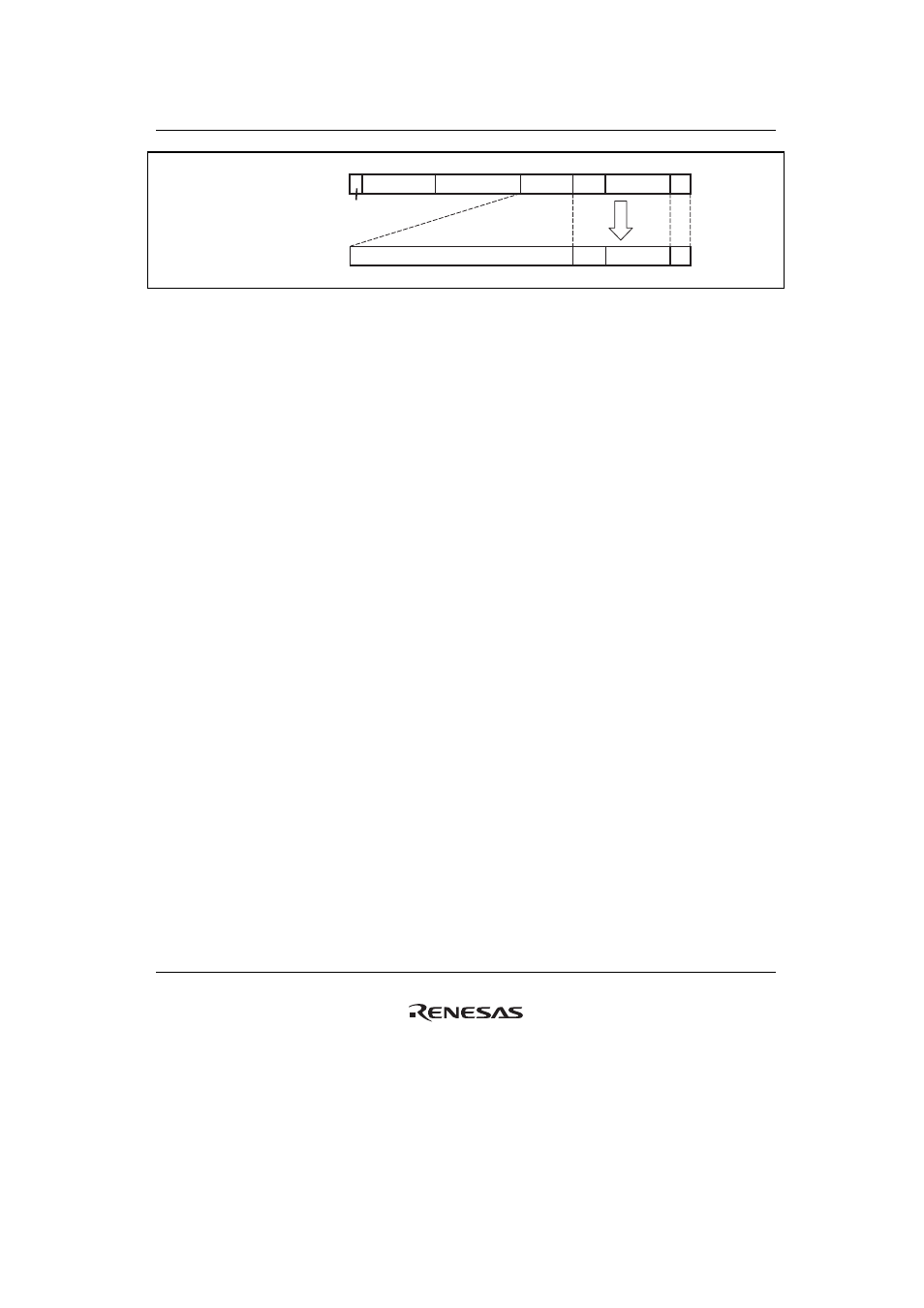

31 30 24

16

23

15

1110

8 7

2 1 0

Configuration address

register

PCI bus address

Reserved

Bus No.

Function

No.

Register No. 0 0

0 0

Only one bit is set to 1.

31

1110

8 7

2 1 0

Enable bit

0: Disabled

1: Enabled

Device No.

Figure 13.17 Address Generation for Type 0 Configuration Access

In configuration accesses, no interrupt is generated by a PCI master abort (no device connected).

A configuration write will end normally. A configuration read will return a value of 0.

(3)

Arbitration

In host mode, the PCI bus arbiter in the PCIC is activated.

The PCIC supports four external masters (four pairs of

REQ and GNT).

If the bus usage is simultaneously requested by two devices or more, the bus arbiter accepts the

request of the highest priority device.

The PCI bus arbiter supports two modes to determine the device priority: (1) fixed priority and (2)

pseudo-round-robin. The mode is selected by the BMAM bit in PCICR.

In the following description, the device n indicates a PCI device that uses

REQn.

(a) Fixed Priority: When the BMAM bit in PCICR is cleared to 0, the priorities of devices are

fixed by the default as follows:

PCIC > device 0 > device 1 > device 2 > device 3

The PCIC has the priority to use the bus in comparison with other devices.

(b) Pseudo-Round-Robin: When the BMAM bit in PCICR is set to 1, the most recently permitted

device is assigned as the lowest priority.

The initial priority is the same as that of the fixed priority mode.

After the device 1 requires the bus and transfer data and the request is permitted, the priority

changes as follows:

PCIC > device 0 > device 2 > device 3 > device 1