7 status register (sistr) – Renesas SH7781 User Manual

Page 1142

22. Serial I/O with FIFO (SIOF)

Rev.1.00 Jan. 10, 2008 Page 1112 of 1658

REJ09B0261-0100

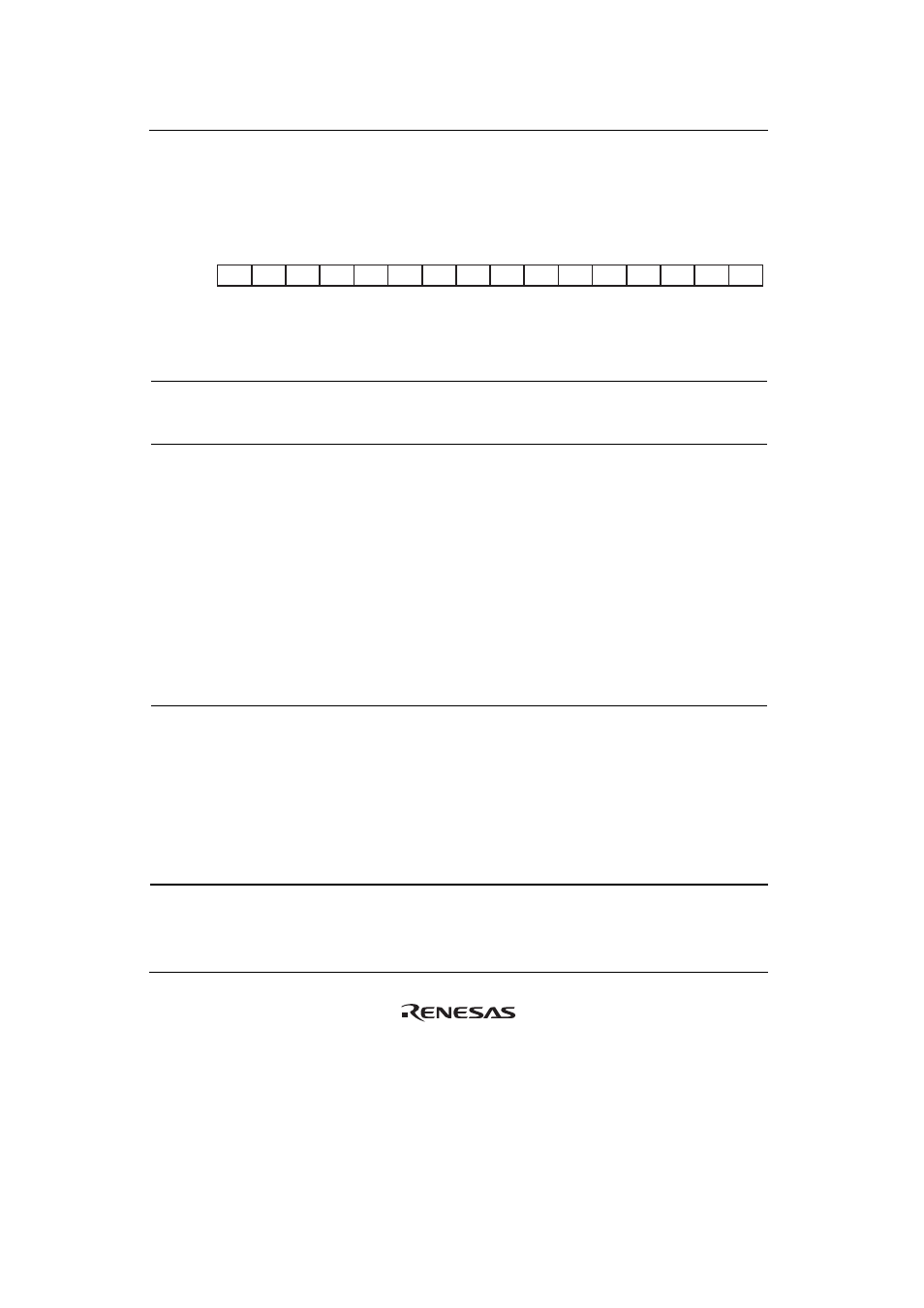

22.3.7

Status Register (SISTR)

SISTR is a 16-bit readable/writable register that indicates the SIOF state. Each bit in this register

becomes an SIOF interrupt source when the corresponding bit in SIIER is set to 1.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

RFOVF

RFUDF

TFUDF

TFOVF

FSERR

SAERR

—

—

RDREQ

RFFUL

RCRDY

—

TDREQ

TFEMP

—

TCRDY

R/W

R/W

R/W

R/W

R/W

R/W

R

R

R

R

R

R

R

R

R

R

BIt:

Initial value:

R/W:

Bit Bit

Name

Initial

Value R/W Description

15

⎯ 0

R

Reserved

This bit is always read as 0. The write value should

always be 0.

14

TCRDY

0

R

Transmit Control Data Ready

0: Indicates that writing to SITCR is disabled

1: Indicates that writing to SITCR is enabled

• If SITCR is written to when this bit is cleared to 0,

SITCR is overwritten to and the previous contents of

SITCR are not output from the SIOF_TXD pin.

• This bit is valid when the TXE bit in SITCR is set to

1.

• This bit indicates the SIOF state. If SITCR is written

to, this bit is automatically cleared to 0.

• To enable the issuance of this interrupt source, set

the TCRDYE bit in SIIER to 1.

13 TFEMP

0 R Transmit

FIFO

Empty

0: Indicates that transmit FIFO is not empty

1: Indicates that transmit FIFO is empty

• This bit is valid when the TXE bit in SICTR is 1.

• This bit indicates the SIOF state. If SITDR is written

to, this bit is automatically cleared to 0.

• To enable the issuance of this interrupt source, set

the TFEMPE bit in SIIER to 1.