Renesas SH7781 User Manual

Page 680

13. PCI Controller (PCIC)

Rev.1.00 Jan. 10, 2008 Page 650 of 1658

REJ09B0261-0100

Subsequently, after the PCIC requires the bus and transfer data and the request is permitted, the

priority changes as follows:

Device 0 > device 2 > device 3 > device 1 > PCIC

Then, after the device 3 requires the bus and transfer data and the request is permitted, the priority

changes as follows:

Device 0 > device 2 > device 1 > PCIC > device 3

(4)

Interrupts

• The PCIC has 10 interrupts (these signals are connected to the INTC of this LSI)

• Interrupts are enabled/disabled and their priority levels are specified by the INTC of this LSI

• When the PCIC operates in normal mode, INTA output is available as an interrupt to the host

device on the PCI bus. The

INTA pin can be set to be asserted or negated by the IOCS bit in

PCICR.

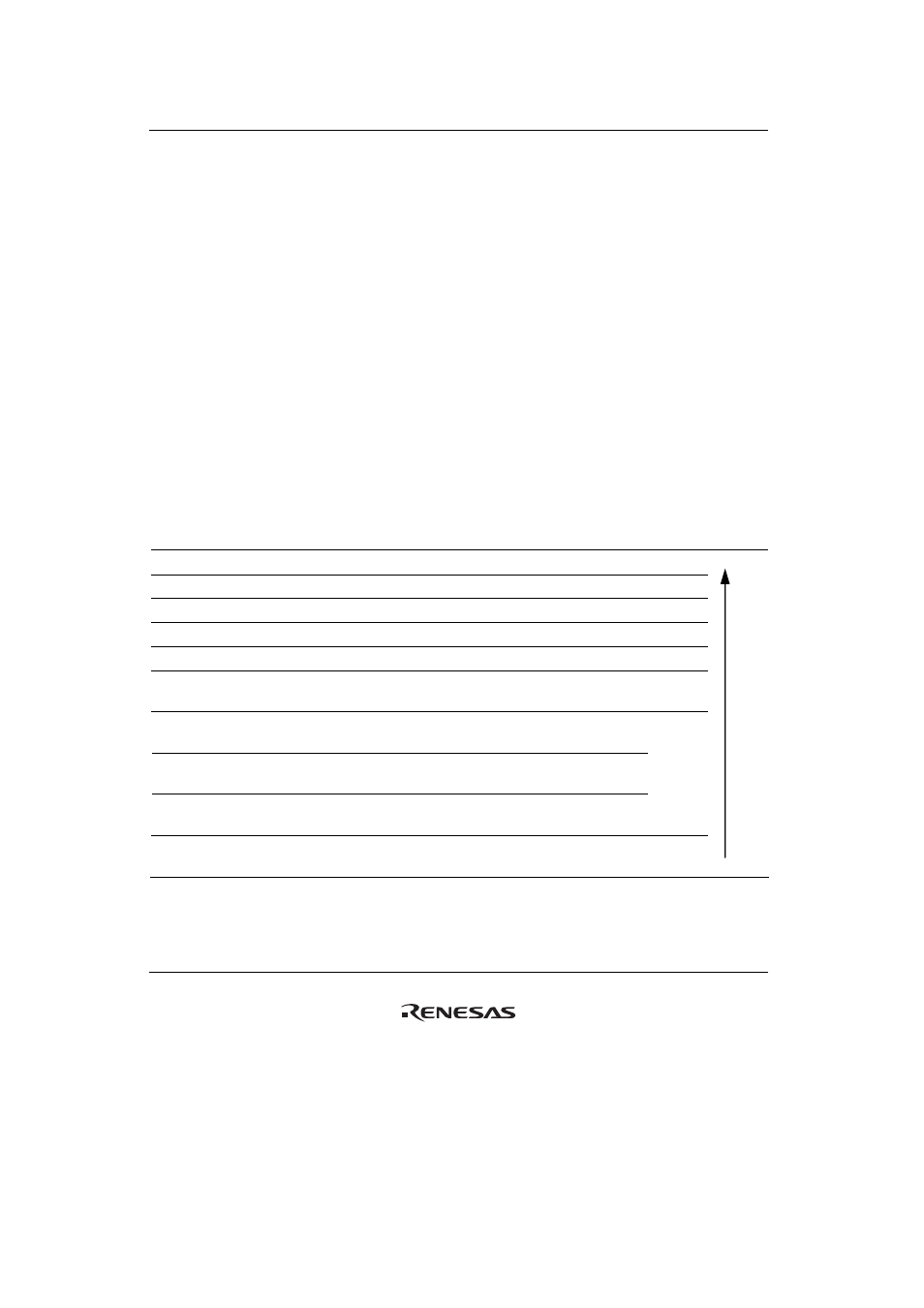

Table 13.6 Interrupt Priority

Signal Interrupt

Source

INTEVT

Priority

PCISERR

SERR assertion detected in host mode

H'A00

High

PCIINTA

PCI interrupt A (

INTA) assertion detected in host mode

H'A20

PCIINTB

PCI interrupt B (

INTB) assertion detected in host mode

H'A40

PCIINTC

PCI interrupt C (

INTC) assertion detected in host mode

H'A60

PCIINTD

PCI interrupt D (

INTD) assertion detected in host mode

H'A80

PCIEER

A PCI error occurs. Generated by PCIIR and PCIAINT.

(Maskable)

H'AA0

PCIPWD3

Power state transition to D3. Generated by PCIPINT.

(Maskable)

PCIPWD2

Power state transition to D2. Generated by PCIPINT.

(Maskable)

PCIPWD1

Power state transition to D1. Generated by PCIPINT.

(Maskable)

H'AC0

PCIPWD0

Power state transition to D0. Generated by PCIPINT.

(Maskable)

H'AE0

Low