4 register descriptions – Renesas SH7781 User Manual

Page 392

11. Local Bus State Controller (LBSC)

Rev.1.00 Jan. 10, 2008 Page 362 of 1658

REJ09B0261-0100

11.4

Register Descriptions

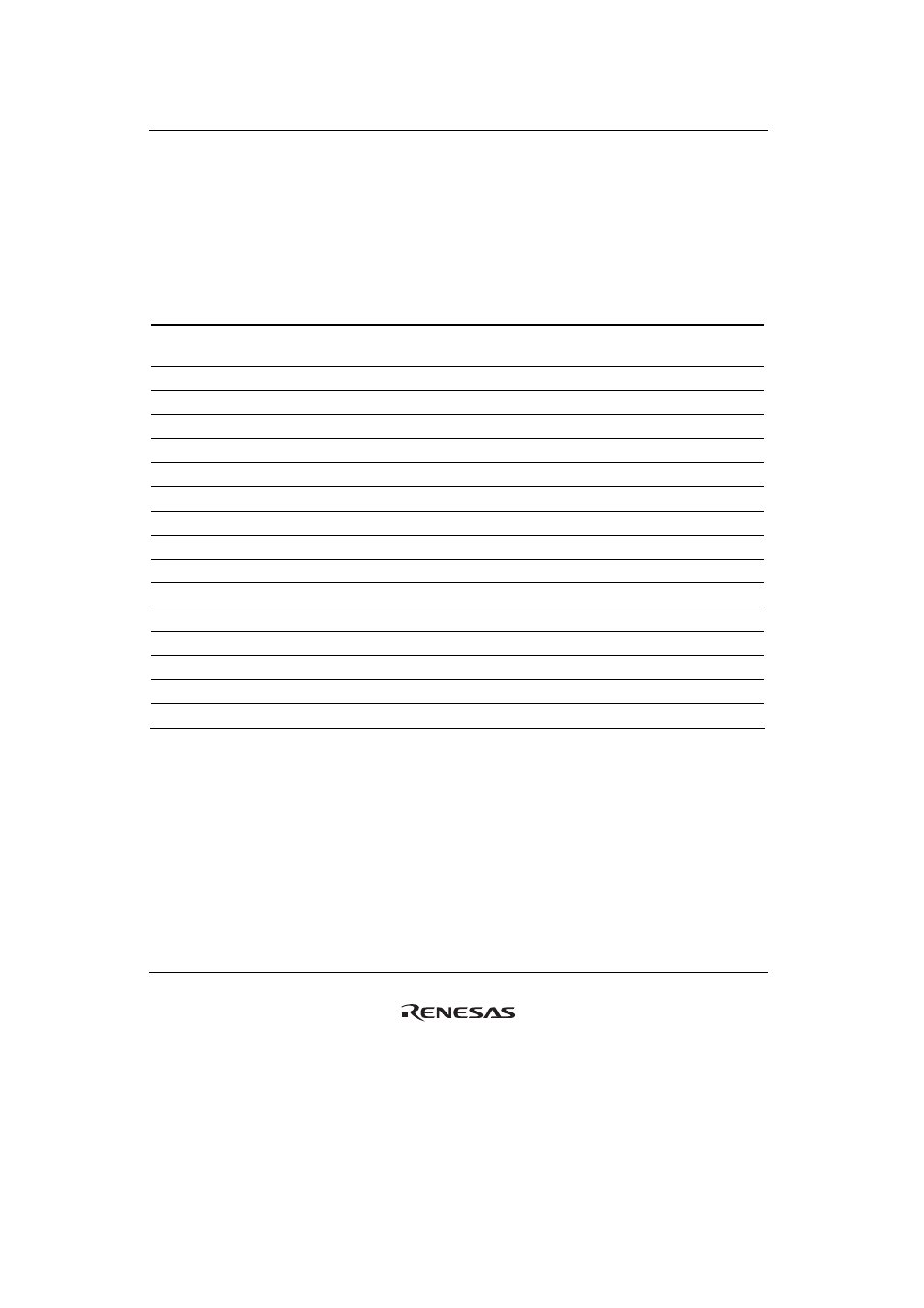

Table 11.5 shows registers for the LBSC. These registers control the interface with each memory,

wait state, etc.

Table 11.5 Register Configuration (1)

Register Name

Abbrev.

R/W

P4 Address

Area 7

Address

Access

Size*

Sync

Clock

Memory Address Map Select

Register

MMSELR R/W H'FC40

0020

H'1C40

0020

32

SHck

Bus Control Register

BCR

R/W

H'FF80 1000 H'1F80 1000 32

Bck

CS0 Bus Control Register

CS0BCR

R/W

H'FF80 2000 H'1F80 2000 32

Bck

CS1 Bus Control Register

CS1BCR

R/W

H'FF80 2010 H'1F80 2010 32

Bck

CS2 Bus Control Register

CS2BCR

R/W

H'FF80 2020 H'1F80 2020 32

Bck

CS4 Bus Control Register

CS4BCR

R/W

H'FF80 2040 H'1F80 2040 32

Bck

CS5 Bus Control Register

CS5BCR

R/W

H'FF80 2050 H'1F80 2050 32

Bck

CS6 Bus Control Register

CS6BCR

R/W

H'FF80 2060 H'1F80 2060 32

Bck

CS0 Wait Control Register

CS0WCR

R/W

H'FF80 2008 H'1F80 2008 32

Bck

CS1 Wait Control Register

CS1WCR

R/W

H'FF80 2018 H'1F80 2018 32

Bck

CS2 Wait Control Register

CS2WCR

R/W

H'FF80 2028 H'1F80 2028 32

Bck

CS4 Wait Control Register

CS4WCR

R/W

H'FF80 2048 H'1F80 2048 32

Bck

CS5 Wait Control Register

CS5WCR

R/W

H'FF80 2058 H'1F80 2058 32

Bck

CS6 Wait Control Register

CS6WCR

R/W

H'FF80 2068 H'1F80 2068 32

Bck

CS5 PCMCIA Control Register

CS5PCR

R/W

H'FF80 2070 H'1F80 2070 32

Bck

CS6 PCMCIA Control Register

CS6PCR

R/W

H'FF80 2080 H'1F80 2080 32

Bck

Note: Do not access with except the specified access size.