Renesas SH7781 User Manual

Page 341

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 311 of 1658

REJ09B0261-0100

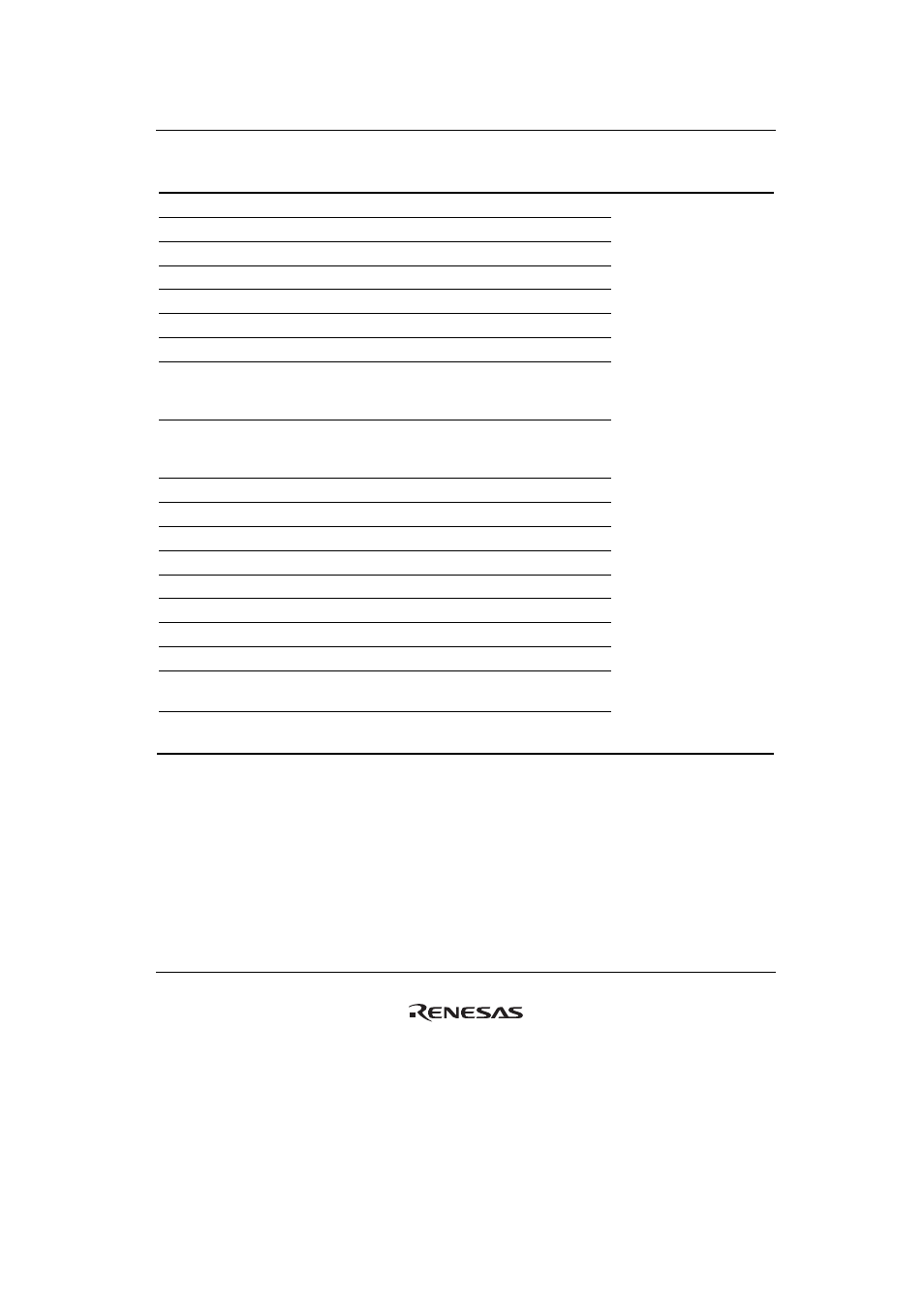

Bit

Initial

Value R/W Source

Function

Description

18

1

R/W PCIC (4)

Masks the PCIINTD interrupt

17

1

R/W PCIC (3)

Masks the PCIINTC interrupt

16

1

R/W PCIC (2)

Masks the PCIINTB interrupt

15

1

R/W PCIC (1)

Masks the PCIINTA interrupt

14

1

R/W PCIC (0)

Masks the PCISERR interrupt

13

1

R/W HAC channel 1 Masks the HAC channel 1 interrupt

12

1

R/W HAC channel 0 Masks the HAC channel 0 interrupt

11

1

R/W DMAC (1)

Masks DMAC channels 6 to 11

interrupts and address error

interrupt

Masks interrupt to each

on-chip peripheral

module

[When written]

0: Invalid

1: Interrupts are masked

[When read]

0: Not masked

1: Masked

10

1

R/W DMAC (0)

Masks DMAC channels 0 to 5

interrupts and address error

interrupt

9

1

R/W H-UDI

Masks the H-UDI interrupt

8

1

R/W WDT

Masks the WDT interrupt

7

1

R/W SCIF channel 5 Masks SCIF channel 5 interrupt

6

1

R/W SCIF channel 4 Masks SCIF channel 4 interrupt

5

1

R/W SCIF channel 3 Masks SCIF channel 3 interrupt

4

1

R/W SCIF channel 2 Masks SCIF channel 2 interrupt

3

1

R/W SCIF channel 1 Masks SCIF channel 1 interrupt

2

1

R/W SCIF channel 0 Masks SCIF channel 0 interrupt

1 1 R/W

TMU

channels

3 to 5

Masks TMU channels 3 to 5

interrupts

0 1 R/W

TMU

channels

0 to 2

Masks TMU channels 0 to 2

interrupts