3 register descriptions, Table 26.2 register configuration (2) – Renesas SH7781 User Manual

Page 1330

26. Serial Sound Interface (SSI) Module

Rev.1.00 Jan. 10, 2008 Page 1300 of 1658

REJ09B0261-0100

26.3

Register Descriptions

The SSI has the following registers. In this manual, the register description is not discriminated

by the channel.

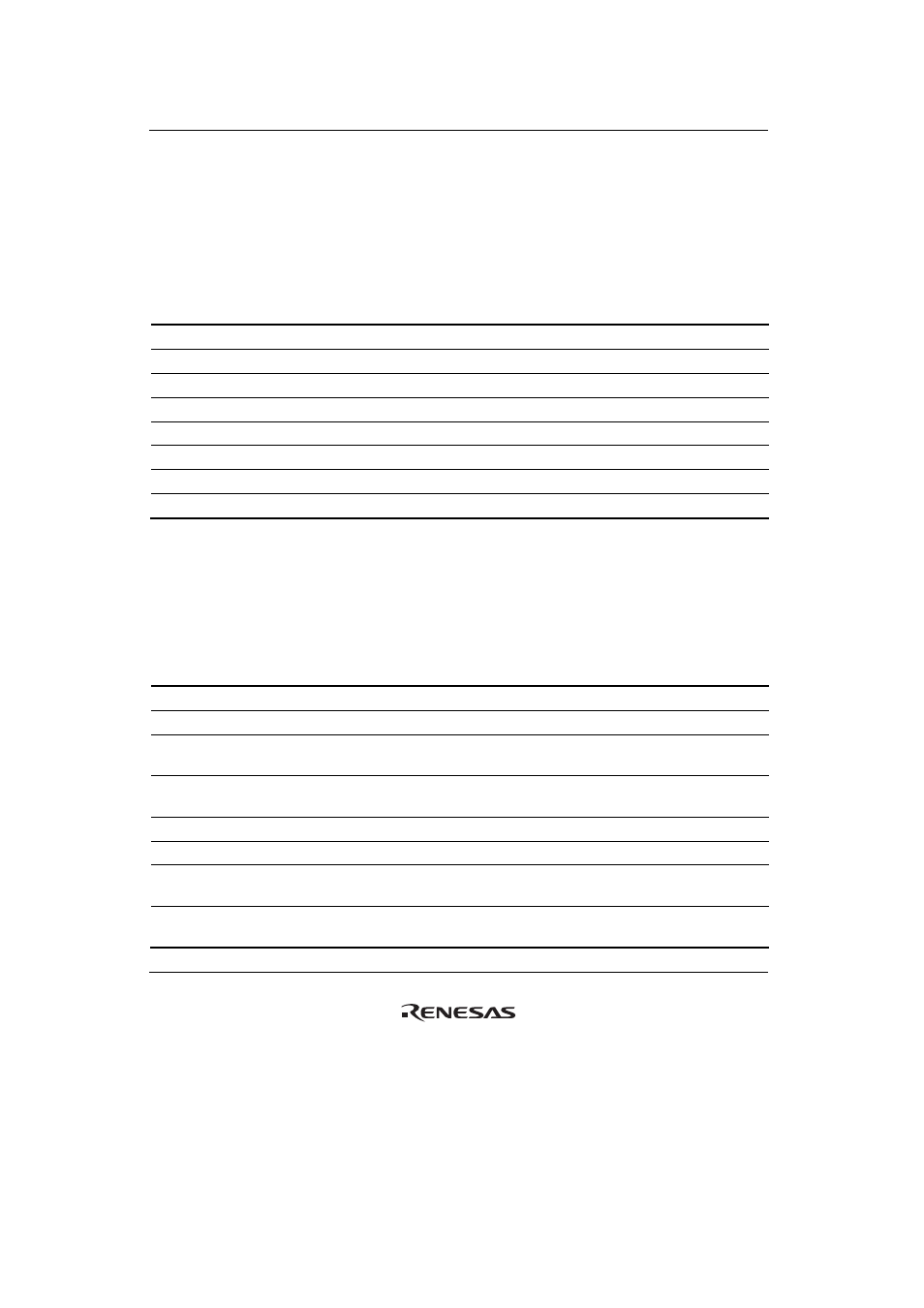

Table 26.2 Register Configuration (1)

Channel Register Name

Abbrev.

R/W

P4 Address

Area 7

Address Size

Sync

Clock

0

Control register 0

SSICR0

R/W

H'FFE0 0000

H'1FE0 0000

32

Pck

0

Status register 0

SSISR0

R/W* H'FFE0

0004 H'1FE0

0004 32 Pck

0

Transmit data register 0

SSITDR0

R/W

H'FFE0 0008

H'1FE0 0008

32

Pck

0

Receive data register 0

SSIRDR0

R

H'FFE0 000C

H'1FE0 000C

32

Pck

1

Control register 1

SSICR1

R/W

H'FFE1 0000

H'1FE1 0000

32

Pck

1

Status register 1

SSISR1

R/W* H'FFE1

0004 H'1FE1

0004 32 Pck

1

Transmit data register 1

SSITDR1

R/W

H'FFE1 0008

H'1FE1 0008

32

Pck

1

Receive data register 1

SSIRDR1

R

H'FFE1 000C

H'1FE1 000C

32

Pck

Note: Bits 26 and 27 of this register is readable/writable. The other bits are read only. For

details, see section 26.3.2, Status Register (SSISR).

Table 26.2 Register Configuration (2)

Channel Register

Name Abbrev.

Power-on

Reset by

PRESET Pin/

WDT/H-UDI

Manual Reset

by WDT/

Multiple

Exception

Sleep by

SLEEP

Instruction

Module

Standby

Deep

Sleep

0

Control register 0 SSICR0

H'0000 0000

H'0000 0000

Retained

Retained Retained

0

Status register 0

SSISR0

H'0200 0003

H'0200 0003

Retained

Retained Retained

0 Transmit

data

register 0

SSITDR0

H'0000 0000

H'0000 0000

Retained

Retained Retained

0 Receive

data

register 0

SSIRDR0

H'0000 0000

H'0000 0000

Retained

Retained Retained

1

Control register 1 SSICR1

H'0000 0000

H'0000 0000

Retained

Retained Retained

1

Status register 1

SSISR1

H'0200 0003

H'0200 0003

Retained

Retained Retained

1 Transmit

data

register 1

SSITDR1

H'0000 0000

H'0000 0000

Retained

Retained Retained

1 Receive

data

register 1

SSIRDR1

H'0000 0000

H'0000 0000

Retained

Retained Retained