7 tx status register (hactsr) – Renesas SH7781 User Manual

Page 1309

25. Audio Codec Interface (HAC)

Rev.1.00 Jan. 10, 2008 Page 1279 of 1658

REJ09B0261-0100

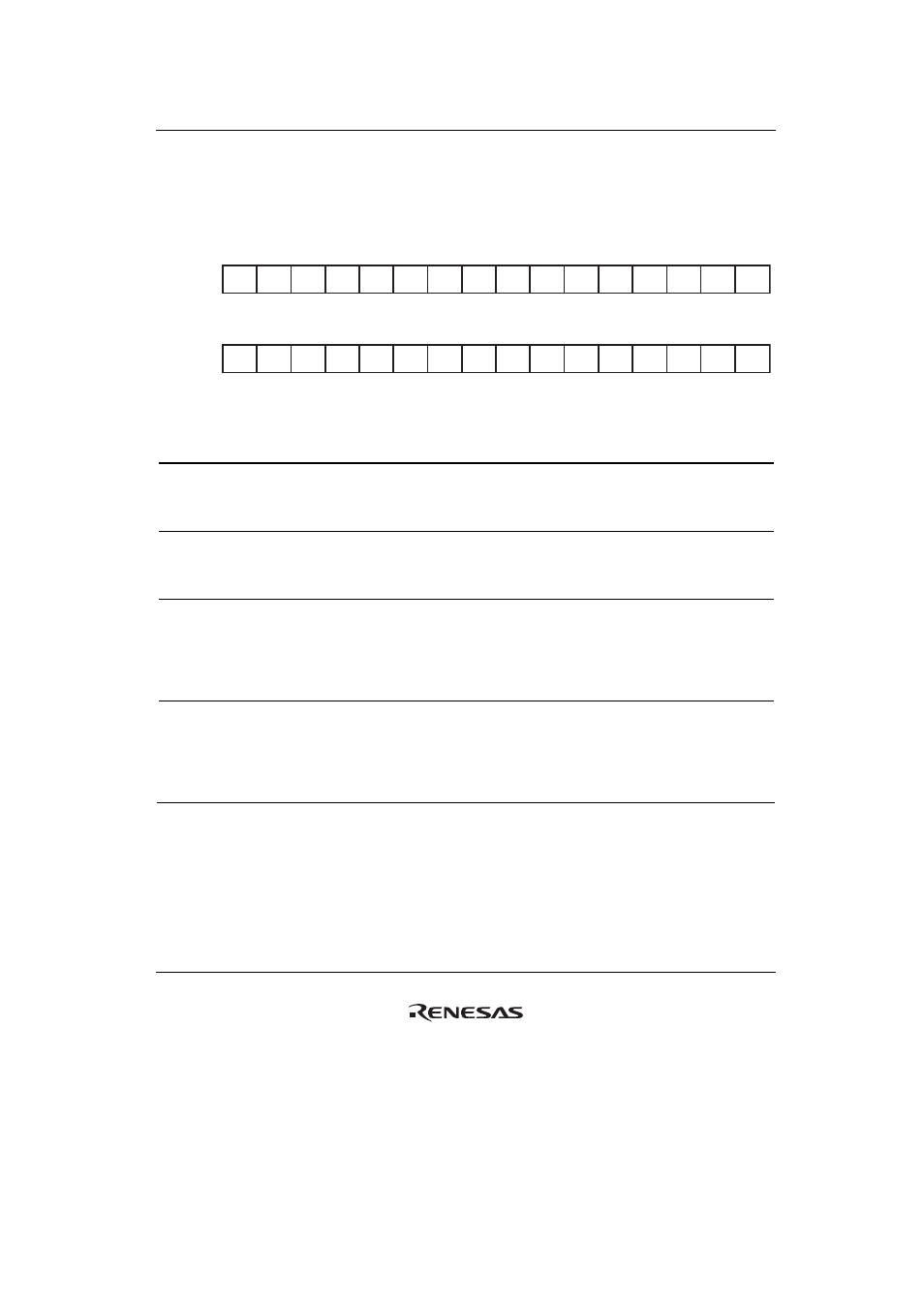

25.3.7

TX Status Register (HACTSR)

HACTSR is a 32-bit read/write register that indicates the status of the HAC TX controller. Writing

0 to the bit will initialize it.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

Bit:

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

Initial value:

R/W

R/W

R/W

R/W

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R/W:

Bit:

Initial value:

R/W:

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

R

R

R

R

R

R

R/W

R/W

PLT

FUN

PRT

FUN

⎯

⎯

⎯

⎯

⎯

⎯

PLT

FRQ

CMD

DMT

CMD

AMT

PRT

FRQ

0

Bit Bit

Name

Initial

Value R/W*

2

Description

31

CMDAMT

1

R/W

Command Address Empty

0: CSAR TX buffer contains untransmitted data.

1: CSAR TX buffer is empty and ready to store data.*

1

30

CMDDMT

1

R/W

Command Data Empty

0: CSDR TX buffer contains untransmitted data.

1: CSDR TX buffer is empty and ready to store data. *

1

29

PLTFRQ

1

R/W

PCML TX Request

0: PCML TX buffer contains untransmitted data.

1: PCML TX buffer is empty and needs to store data. In

DMA mode, writing to HACPCML will automatically

clear this bit to 0.

28

PRTFRQ

1

R/W

PCMR TX Request

0: PCMR TX buffer contains untransmitted data.

1: PCMR TX buffer is empty and needs to store data. In

DMA mode, writing to HACPCMR will automatically

clear this bit to 0.