Renesas SH7781 User Manual

Page 1413

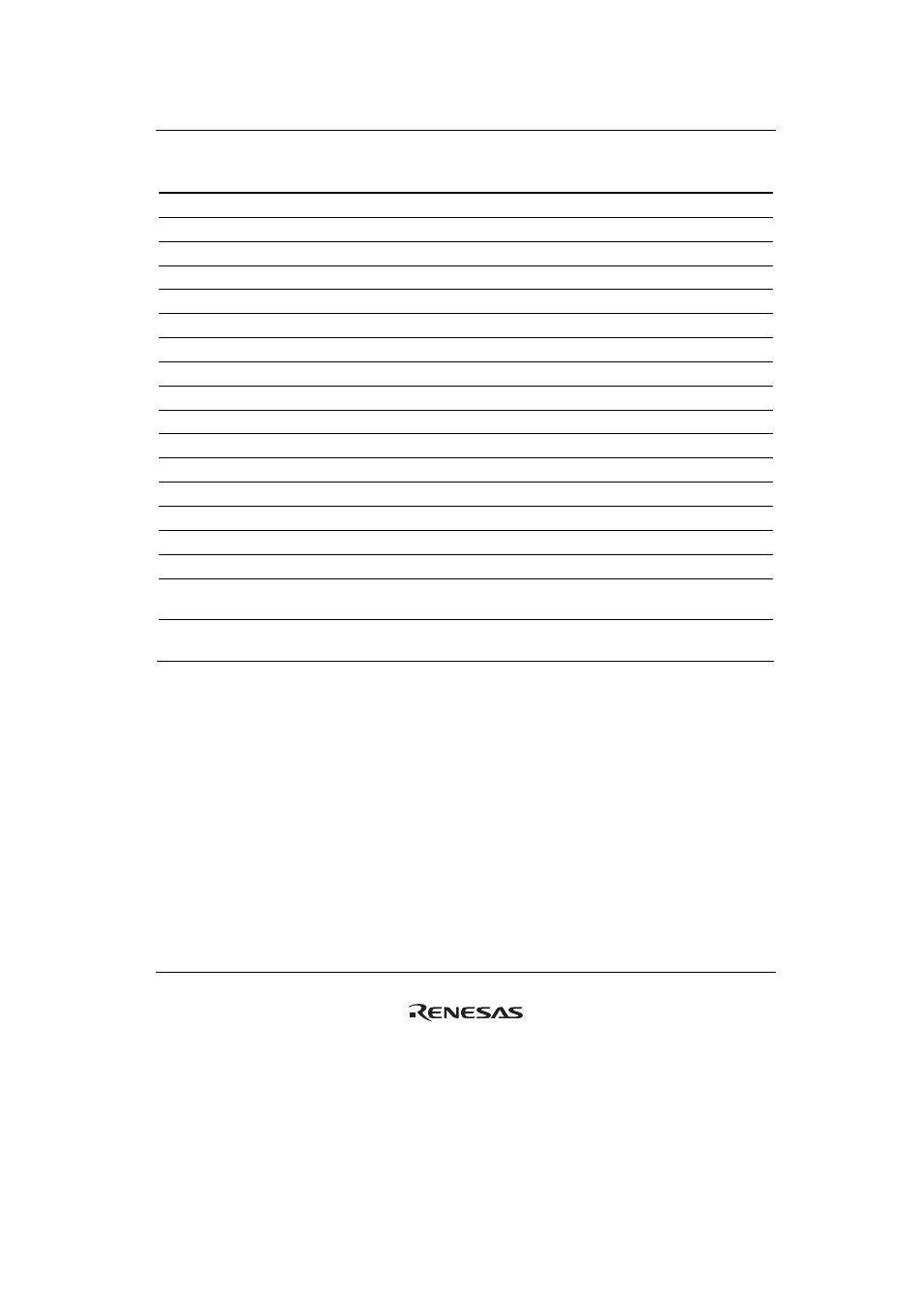

28. General Purpose I/O Ports (GPIO)

Rev.1.00 Jan. 10, 2008 Page 1383 of 1658

REJ09B0261-0100

Register Name

Abbrev.

R/W

P4 Address

*

1

Area 7

Address

*

1

Access

Size

*

2

Sync

Clock

Port K data register

PKDR

R/W

H'FFE7 0032

H'1FE7 0032

8

Pck

Port L data register

PLDR

R/W

H'FFE7 0034

H'1FEA 0034

8

Pck

Port M data register

PMDR

R/W

H'FFE7 0036

H'1FEA 0036

8

Pck

Port N data register

PNDR

R/W

H'FFE7 0038

H'1FEA 0038

8

Pck

Port P data register

PPDR

R/W

H'FFE7 003A

H'1FEA 003A

8

Pck

Port Q data register

PQDR

R/W

H'FFE7 003C

H'1FEA 003C

8

Pck

Port R data register

PRDR

R/W

H'FFE7 003E

H'1FEA 003E

8

Pck

Port E pull-up control register

PEPUPR

R/W

H'FFE7 0048

H'1FEA 0048

8

Pck

Port H pull-up control register

PHPUPR

R/W

H'FFE7 004E

H'1FEA 004E

8

Pck

Port J pull-up control register

PJPUPR

R/W

H'FFE7 0050

H'1FE7 0050

8

Pck

Port K pull-up control register

PKPUPR R/W H'FFE7

0052 H'1FE7

0052 8

Pck

Port L pull-up control register

PLPUPR

R/W

H'FFE7 0054

H'1FE7 0054

8

Pck

Port M pull-up control register

PMPUPR

R/W

H'FFE7 0056

H'1FE7 0056

8

Pck

Port N pull-up control register

PNPUPR

R/W

H'FFE7 0058

H'1FE7 0058

8

Pck

Input pin pull-up control register 1 PPUPR1 R/W H'FFE7

0060 H'1FE7

0060 16

Pck

Input pin pull-up control register 2 PPUPR2 R/W H'FFE7

0062 H'1FE7

0062 16

Pck

Peripheral module select register

1

P1MSELR R/W

H'FFE7

0080

H'1FE7

0080

16

Pck

Peripheral module select register

2

P2MSELR R/W

H'FFE7

0082

H'1FE7

0082

16

Pck

Notes: 1. The P4 area address uses the P4 area of the logical address area. The area 7 address

is accessed from area 7 of the physical address space using the TLB.

2. There are 8-bit and 16-bit registers. The registers must be accessed in the designate

size.