12 receive data assign register (sirdar) – Renesas SH7781 User Manual

Page 1155

22. Serial I/O with FIFO (SIOF)

Rev.1.00 Jan. 10, 2008 Page 1125 of 1658

REJ09B0261-0100

22.3.12

Receive Data Assign Register (SIRDAR)

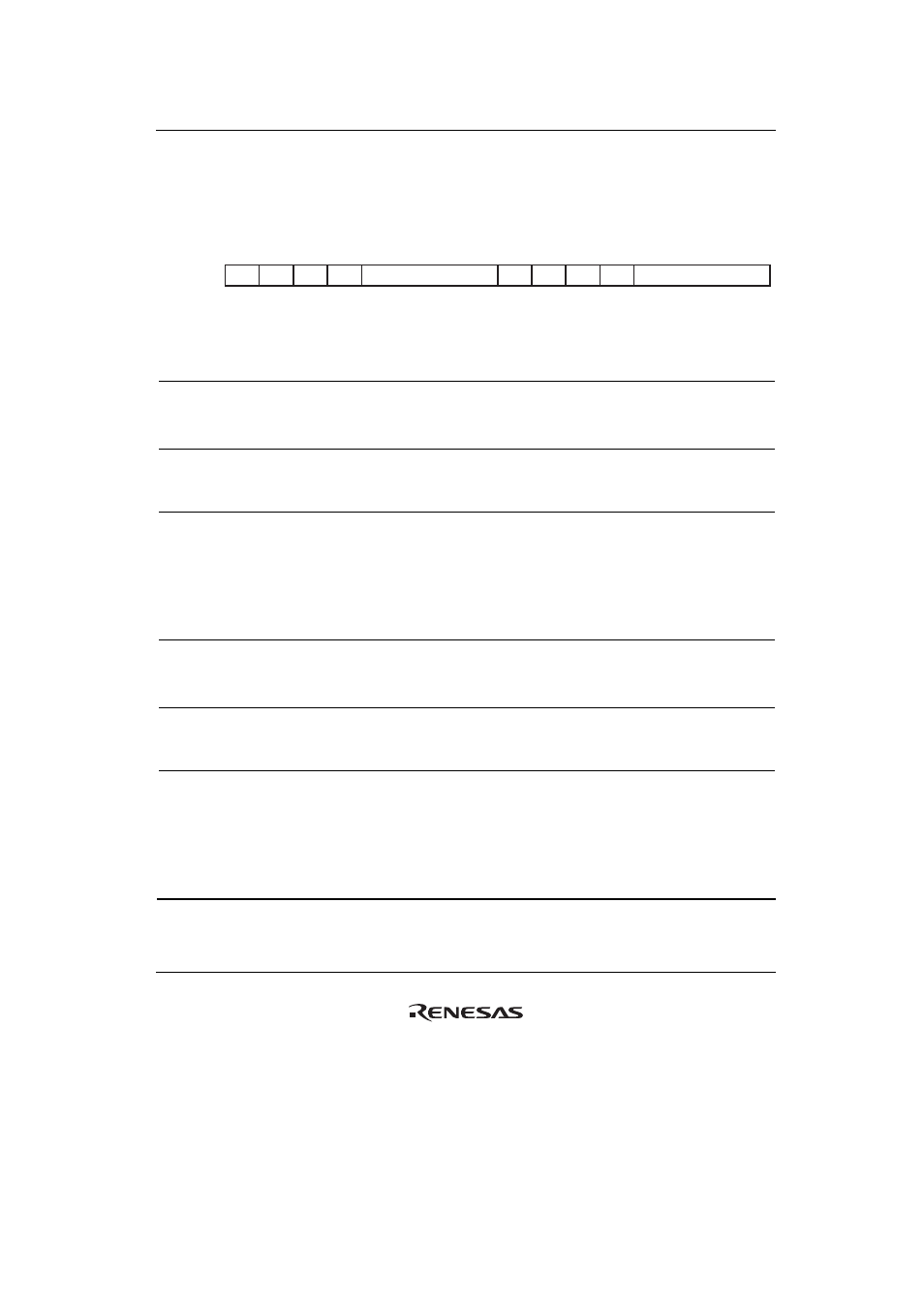

SIRDAR is a 16-bit readable/writable register that specifies the position of the receive data in a

frame.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

RDRA[3:0]

—

—

—

RDRE

RDLA[3:0]

—

RDLE

—

R/W

R/W

R/W

R/W

R

R

R

R/W

R/W

R/W

R/W

R/W

R

R

R/W

R

BIt:

Initial value:

R/W:

—

Bit Bit

Name

Initial

Value R/W Description

15

RDLE

0

R/W

Receive Left-Channel Data Enable

0: Disables left-channel data reception

1: Enables left-channel data reception

14 to 12

⎯ All

0

R

Reserved

These bits are always read as 0. The write value should

always be 0.

11 to 8

RDLA[3:0]

0000

R/W

Receive Left-Channel Data Assigns 3 to 0

These bits specify the position of left-channel data in a

receive frame as B'0000 (0) to B'1110 (14).

1111: Setting prohibited

• Receive data for the left channel is stored in the

SIRDL bit in SIRDR.

7 RDRE

0 R/W

Receive

Right-Channel

Data

Enable

0: Disables right-channel data reception

1: Enables right-channel data reception

6 to 4

⎯ All

0

R

Reserved

These bits are always read as 0. The write value should

always be 0.

3 to 0

RDRA[3:0]

0000

R/W

Receive Right-Channel Data Assigns 3 to 0

These bits specify the position of right-channel data in a

receive frame as B'0000 (0) to B'1110 (14).

1111: Setting prohibited

• Receive data for the right channel is stored in the

SIRDR bit in SIRDR.