Table 10.4 register states in each operating mode – Renesas SH7781 User Manual

Page 305

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 275 of 1658

REJ09B0261-0100

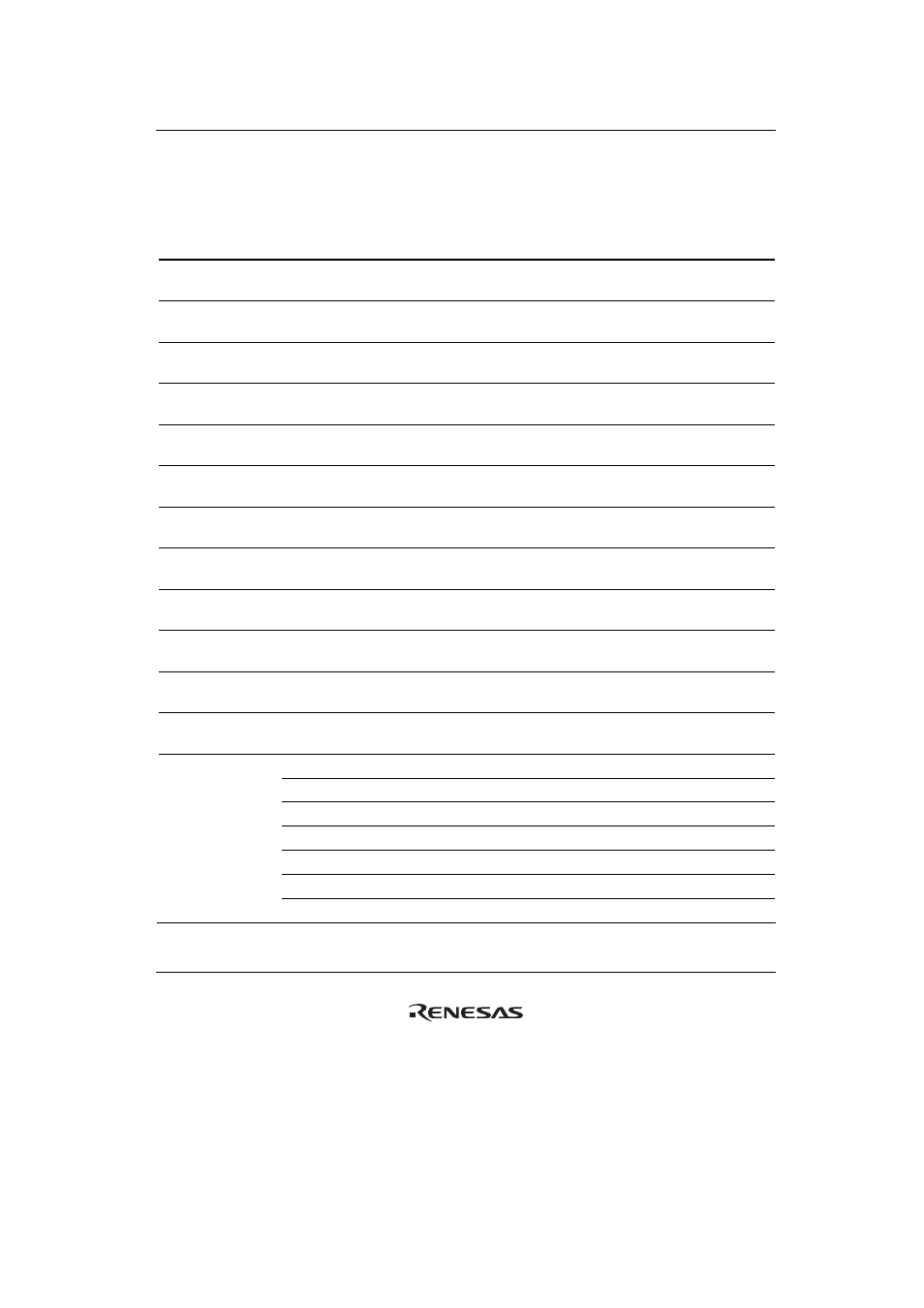

Table 10.4 Register States in Each Operating Mode

Name Abbreviation

Power-on

Reset by

PRESET

Pin/WDT/H-UDI

Manual Reset

by

WDT/Multiple

Exception

Sleep by

SLEEP

Instruction

Deep Sleep by

SLEEP

Instruction

(DSLP

= 1)

Interrupt control

register 0

ICR0 H'x000

0000* H'x000

0000* Retained

Retained

Interrupt control

register 1

ICR1

H'0000 0000

H'0000 0000

Retained

Retained

Interrupt priority

register

INTPRI

H'0000 0000

H'0000 0000

Retained

Retained

Interrupt source

register

INTREQ

H'0000 0000

H'0000 0000

Retained

Retained

Interrupt mask

register 0

INTMSK0

H'0000 0000

H'0000 0000

Retained

Retained

Interrupt mask

register 1

INTMSK1

H'FF00 0000

H'FF00 0000

Retained

Retained

Interrupt mask

register 2

INTMSK2

H'FF00 0000

H'FF00 0000

Retained

Retained

Interrupt mask clear

register 0

INTMSKCLR0

H'xx00 0000

H'xx00 0000

Retained

Retained

Interrupt mask clear

register 1

INTMSKCLR1

H'x000 0000

H'x000 0000

Retained

Retained

Interrupt mask clear

register 2

INTMSKCLR2 H'xxxx

xxxx

H'xxxx xxxx

Retained

Retained

NMI flag control

register

NMIFCR H'x000

0000* H'x000

0000* Retained

Retained

User interrupt mask

level register

USERIMASK

H'0000 0000

H'0000 0000

Retained

Retained

INT2PRI0

H'0000 0000

H'0000 0000

Retained

Retained

INT2PRI1

H'0000 0000

H'0000 0000

Retained

Retained

Interrupt priority

registers

INT2PRI2

H'0000 0000

H'0000 0000

Retained

Retained

INT2PRI3

H'0000 0000

H'0000 0000

Retained

Retained

INT2PRI4

H'0000 0000

H'0000 0000

Retained

Retained

INT2PRI5

H'0000 0000

H'0000 0000

Retained

Retained

INT2PRI6

H'0000 0000

H'0000 0000

Retained

Retained