7 byte control sram interface – Renesas SH7781 User Manual

Page 471

11. Local Bus State Controller (LBSC)

Rev.1.00 Jan. 10, 2008 Page 441 of 1658

REJ09B0261-0100

11.5.7

Byte Control SRAM Interface

The byte control SRAM interface is a memory interface that outputs a byte-select strobe (

WEn) in

both read and write bus cycles. This interface has 16-bit data pins and can be connected to SRAM

having an upper byte select strobe and lower select strobe functions such as UB and LB.

Areas 1 and 4 can be specified as a byte control SRAM interface.

The write timing for the byte control SRAM interface is identical to that of a normal SRAM

interface.

In reading operation, on the other hand, the

WEn pin timing is different. In a read access, only the

WEn signal for the byte being read is asserted. Assertion is synchronized with the falling edge of

the CLKOUT clock in the same way as for the

WEn signal, while negation is synchronized with

the rising edge of the CLKOUT clock in the same way as for the

RD signal.

In 32-byte transfer, a total of 32 bytes are transferred continuously according to the set bus width.

The first access is performed on the data for which there was an access request, and the remaining

accesses are performed in wraparound method according to the set bus width. The bus is not

released during this transfer.

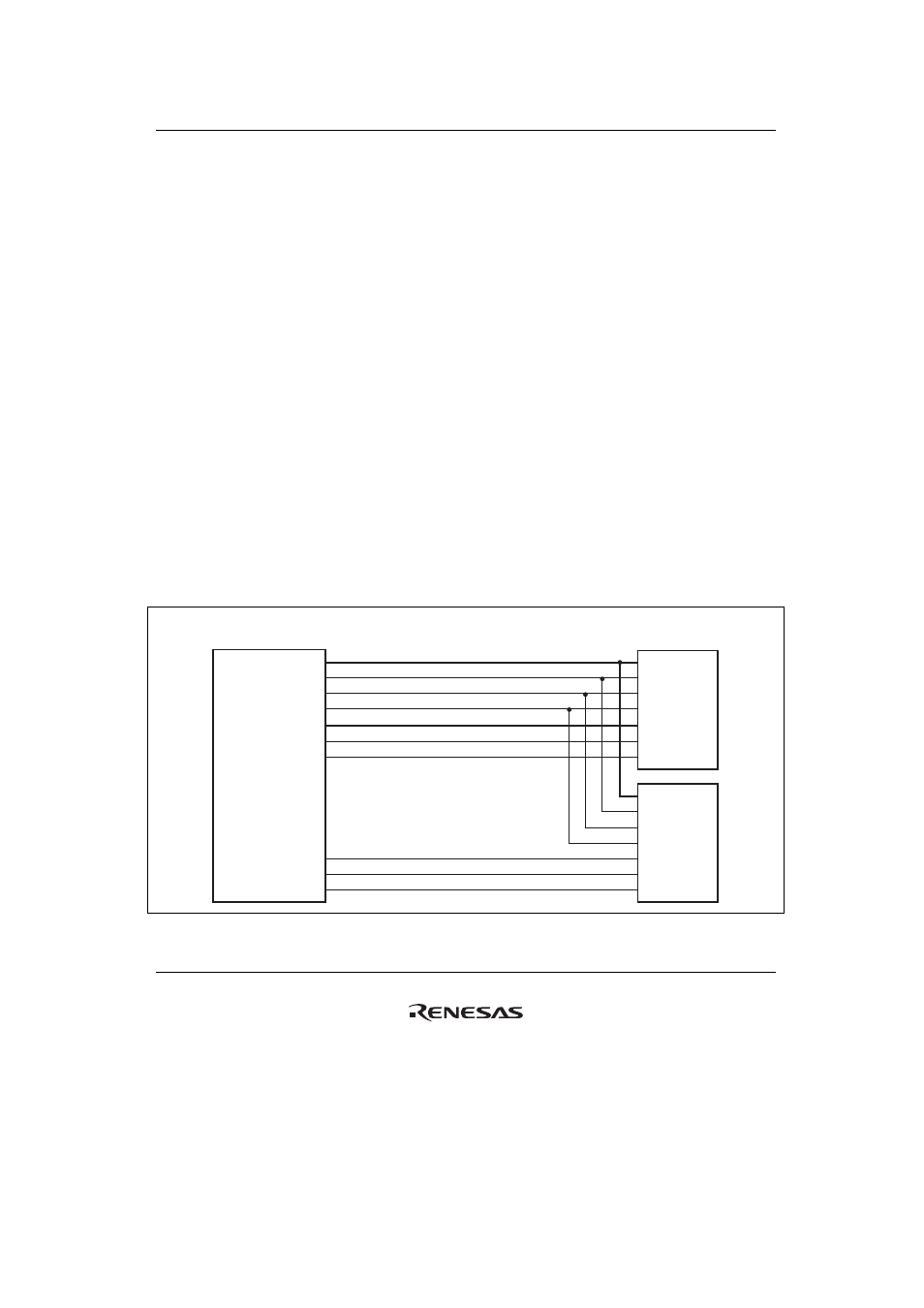

Figures 11.36 and 11.37 show examples of byte control SRAM connections, and figures 11.38 to

11.40 show examples of byte-control SRAM read cycles.

A17 to A2

CSn

RD

R/

W

SH7785

64K

× 16 bits

SRAM

D15 to D0

WE1

WE0

A15 to A0

CS

OE

WE

I/O15 to I/O0

UB

LB

A15 to A0

CS

OE

WE

I/O15 to I/O0

UB

LB

D31 to D16

WE3

WE2

Figure 11.36 Example of Byte Control SRAM with 32-Bit Data Width