7 dreq pin sampling timing – Renesas SH7781 User Manual

Page 751

14. Direct Memory Access Controller (DMAC)

Rev.1.00 Jan. 10, 2008 Page 721 of 1658

REJ09B0261-0100

14.4.7

DREQ Pin Sampling Timing

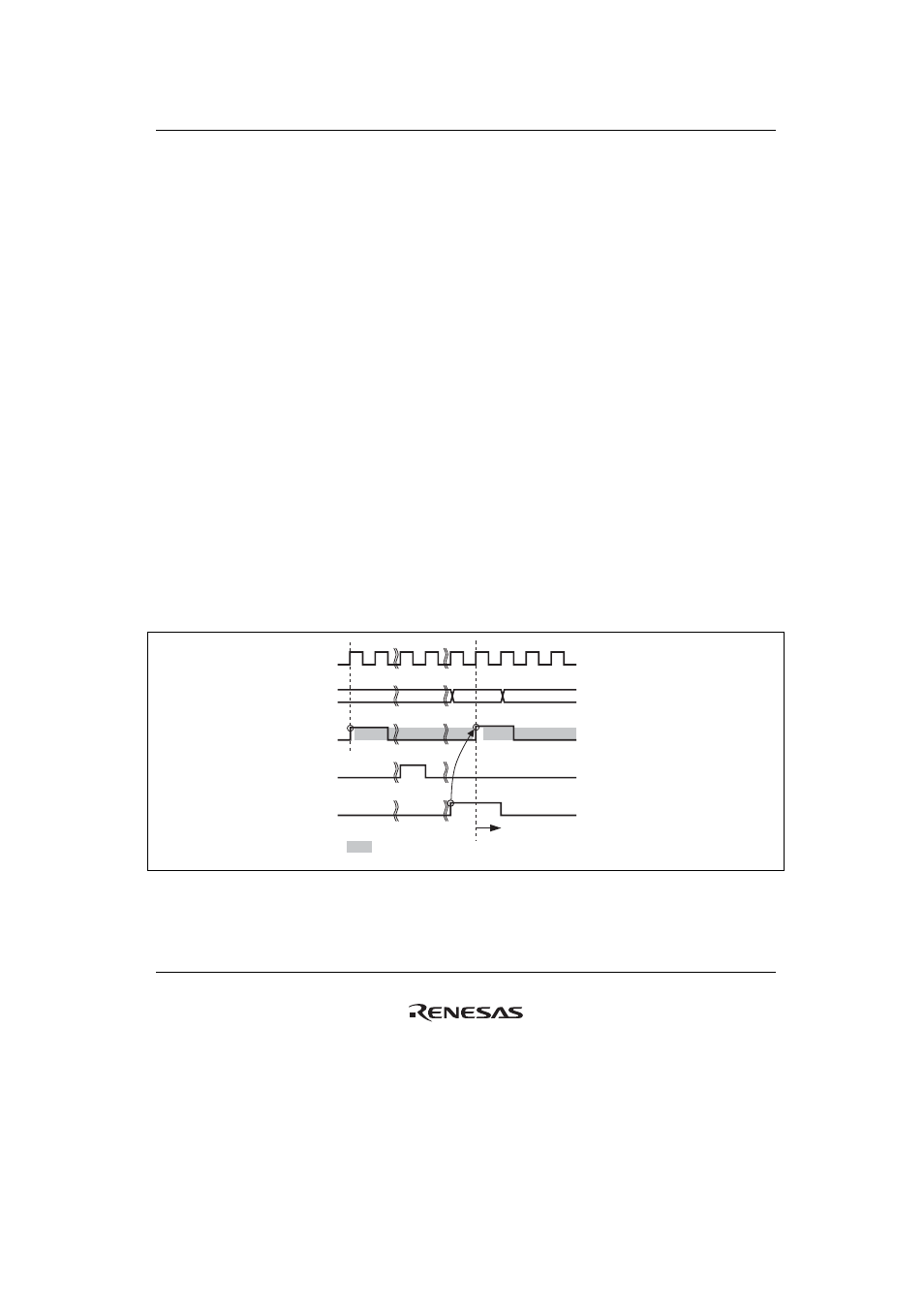

Figures 14.13 to 14.22 show the timing that the DREQ input is sampled in each bus mode.

Figures 14.13, 14.16, and 14.20 show the timing that the DREQ input is sampled when byte

transfer is performed in 8-, 16-, 32-, or 64-bit bus width, word transfer is performed in 16-, 32-, or

64-bit bus width, or longword transfer is performed in 32- or 64-bit bus width. DACK is output

once in DMA1 transfer.

Figures 14.14, 14.17, and 14.21 show the timing that the DREQ input is sampled when word

transfer is performed in 8-bit bus width, longword transfer is performed in 8- or 16-bit bus width,

or 16- or 32-byte transfer is performed in 8-, 16-, 32-, or 64-bit bus width. These figures suppose

that DACK of DMA1 transfer is divided.

Figures 14.15, 14.18, and 14.22 show the timing that the DREQ input is sampled when word

transfer is performed in 8-bit bus width, longword transfer is performed in 8- or 16-bit bus width,

or 16- or 32-byte transfer is performed in 8-, 16-, 32-, or 64-bit bus width. These figures suppose

that DACK of DMA1 transfer is connected.

When word transfer is performed in 8-bit bus width, longword transfer is performed in 8- or 16-bit

bus width, or 16- or 32-byte transfer is performed in 8-, 16-, 32-, or 64-bit bus width, DMA

transfer units are divided into multiple bus cycles. If DMA transfer size is divided into multiple

bus cycles and CS is negated between bus cycles, DACK output is divided, like CS. For details,

see section 11.5.16, Register Settings for Divided-Up

DACKn Output.

CLKOUT

Bus cycle

DREQ

(Rising edge)

DRAK

(High-active)

DACK

(High-active)

: Non-sensitive period

Accepted after one cycle of CLKOUT

at the rising edge of DACK

CPU

DMAC

CPU

1st acceptance

2nd acceptance

Acceptance started

Figure 14.13 Example 1 of DREQ Input Detection in Cycle Steal Mode Edge Detection

(Byte Transfer in 8/16/32/64-Bit Bus Width, Word Transfer in 16/32/64-Bit Bus Width, or

Longword Transfer in 32/64-Bit Bus Width)