Renesas SH7781 User Manual

Page 313

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 283 of 1658

REJ09B0261-0100

(4)

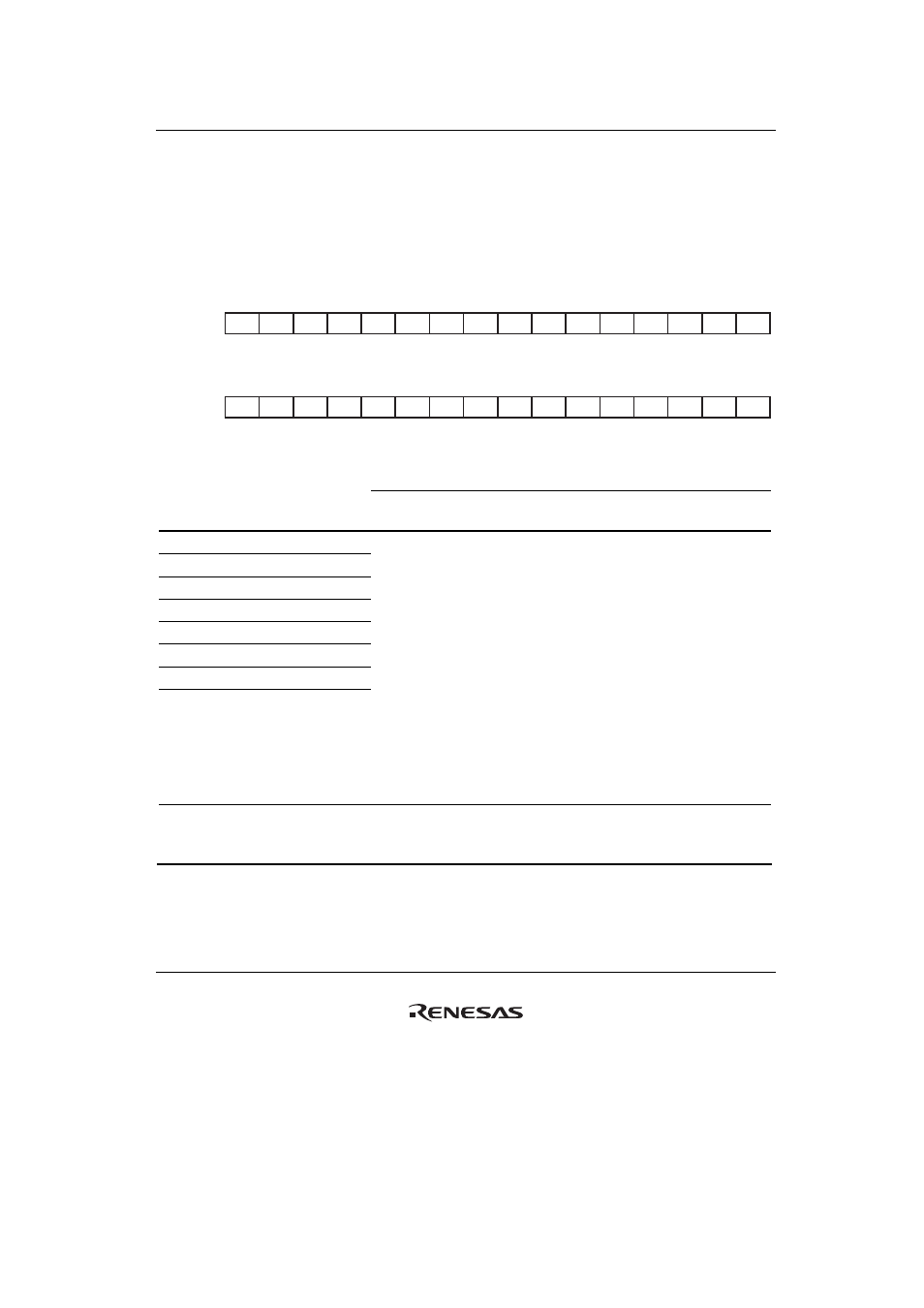

Interrupt Source Register (INTREQ)

INTREQ is a 32-bit readable and conditionally writable register that indicates which of the IRQ

[n] (n = 0 to 7) interrupts is currently asserting a request for the INTC.

Even if an interrupt is masked by the setting in INTPRI or INTMSK0, operation of the

corresponding INTREQ bit is not affected.

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

IR7

IR6

IR5

IR4

IR3

IR2

IR0

IR1

R

R

R

R

R

R

R

R

R/(W)

R/(W)

R/(W)

R/(W)

R/(W)

R/(W)

R/(W) R/(W)

Bit:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Bit:

Initial value:

R/W:

Description

Bit Name

Initial

Value R/W

Edge Detection

(IRQnS = 00 or 01)

*

1

Level Detection

(IRQnS = 10 or 11)

*

1

31 IR0

0 R/(W)

30 IR1

0 R/(W)

29 IR2

0 R/(W)

28 IR3

0 R/(W)

27 IR4

0 R/(W)

26 IR5

0 R/(W)

25 IR6

0 R/(W)

24 IR7

0 R/(W)

[When read]

0: The corresponding IRQ

interrupt request has not

been detected.

1: The corresponding IRQ

interrupt request has been

detected.

[When written]

*

2

When clearing each bit, write a

0 after having read a 1 from it.

Writing 1 to the bit is ignored.

[When read]

(ICR0.LVLMODE = 0)

0: The corresponding interrupt

source has not been

detected.

1: The corresponding interrupt

source has been detected.

[When read]

(ICR0.LVLMODE = 1)

0: The corresponding IRQ

interrupt pin is not asserted.

1: The corresponding IRQ

interrupt pin is asserted, but

the CPU has not accepted

the interrupt request yet.

Writing have no effect.

*

3

23 to 0

⎯ All

0

R Reserved

These bits are always read as 0. The write value should always

be 0.

Notes: 1. n = 0 to 7

2. Write 1 to the bit if it should not be cleared yet.

3. For the method of clearing the IRQ interrupt request that has been detected by level

sensing, refer to section 10.7.3, Clearing IRQ and IRL Interrupt Requests.